“Calculadora com display LCD”

UFSC/CTC/EEL, semestre 2013/2

EEL7020 – Sistemas Digitais

Prof. Eduardo Augusto Bezerra

Prof. Joni da Silva Fraga

Prof. Djones Vinicius Lettnin

Descrição Geral do Problema

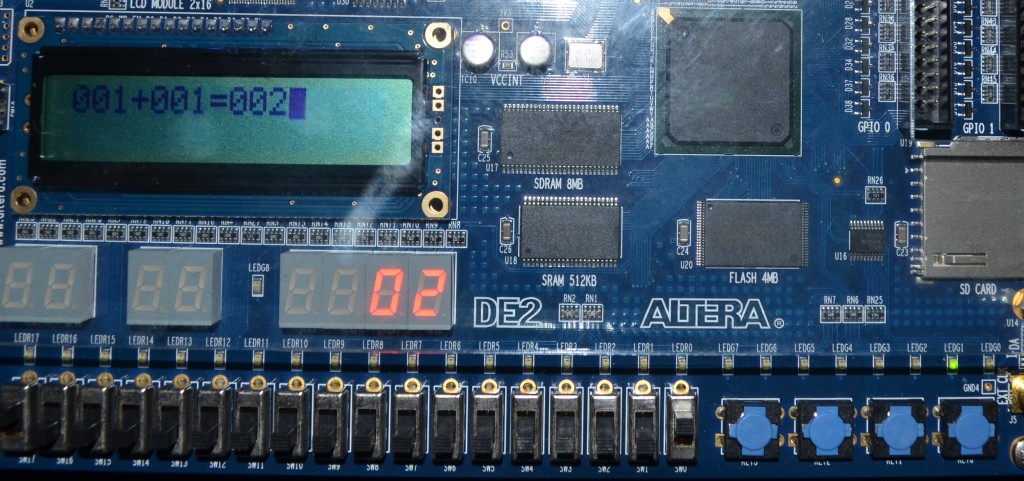

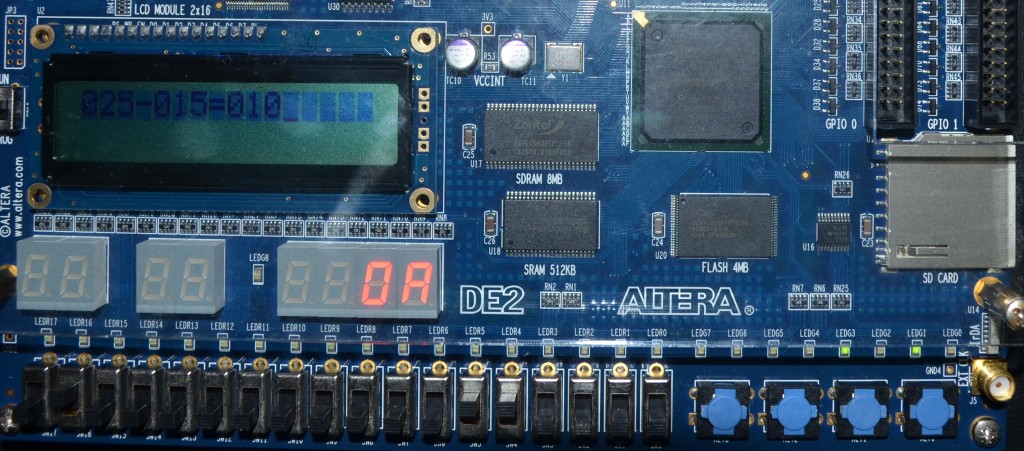

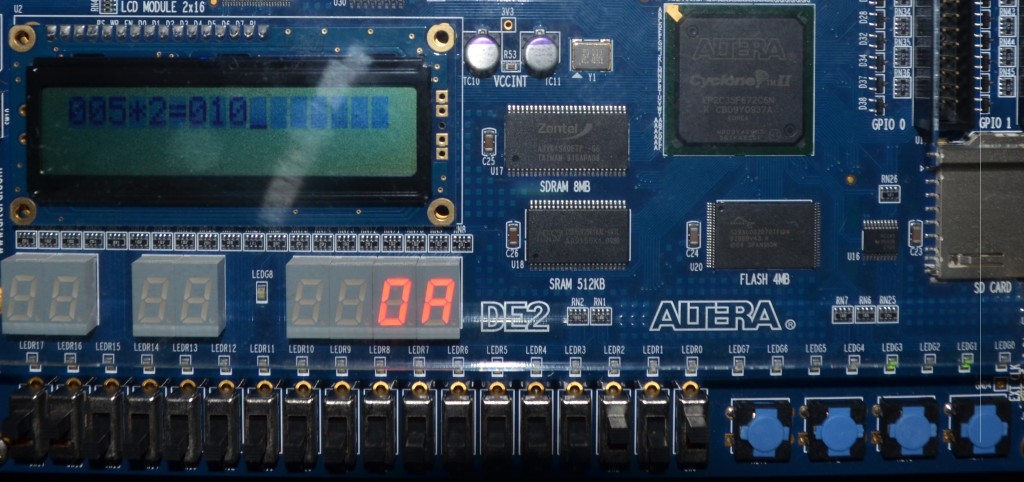

O projeto final consiste na implementação em VHDL para FPGAs de um circuito digital que realize as operações básicas de uma calculadora, apresentando os resultados em hexadecimal (display de 7-segmentos), binário (LEDs), e decimal (display do tipo LCD).

Especificação

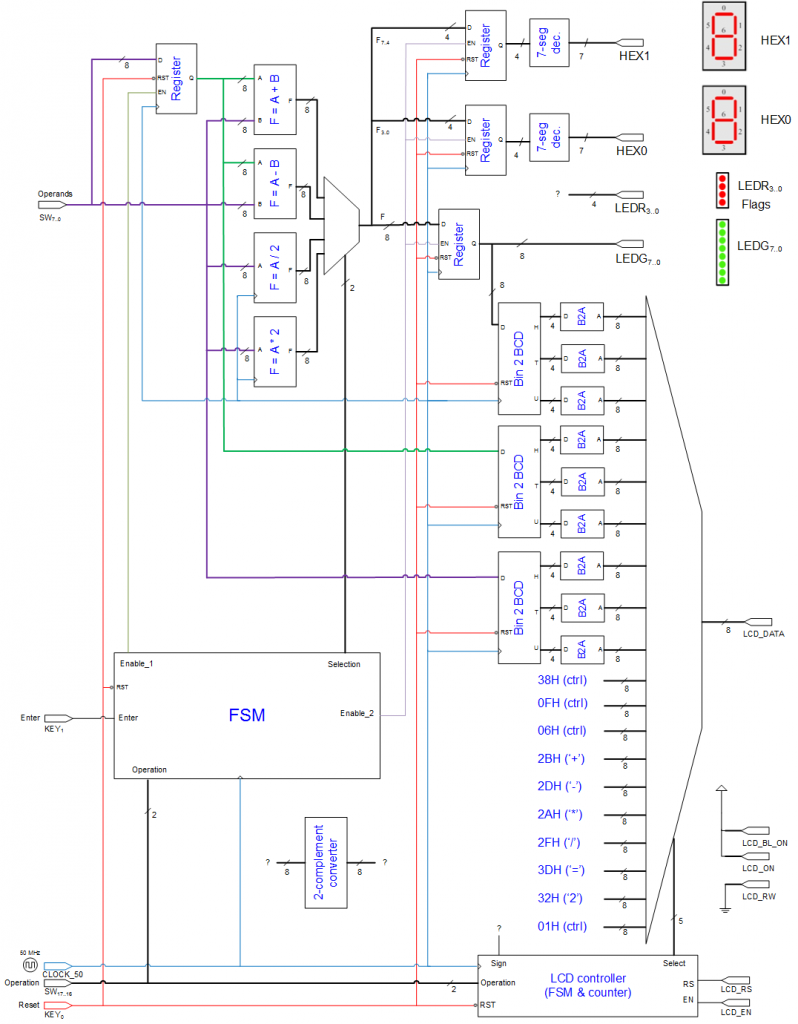

Na Figura 1 está apresentado o diagrama de blocos do circuito a ser implementado. Esse circuito foi parcialmente desenvolvido durante o semestre nas aulas de laboratório, e no trabalho final está sendo solicitada a implementação dos componentes necessários para a apresentação dos resultados das operações no display LCD da plataforma DE2. Apenas o componente que realiza a operação “or” da calculadora desenvolvida nas aulas de laboratório precisará ser substituído por um componente que realiza uma subtração. Inclusive, a FSM da calculadora original pode ser mantida sem alterações, uma vez que a nova operação de subtração também possui dois operandos, de forma semelhante a operação “or”.

A calculadora realiza as seguintes operações:

- Adição de dois operandos de entrada – flags afetados: Zero, Overflow, Carry, e Negativo;

- Subtração de dois operandos de entrada – flags afetados: Zero, Overflow, Carry, e Negativo;

- Divisão por 2 de um operando de entrada – flags afetados: Zero, e Negativo;

- Multiplicação por 2 de um operando de entrada – flags afetados: Zero, Overflow, e Negativo.

As operações são realizadas em números inteiros, com sinal, utilizando a representação de complemento-2.

Para utilizar a calculadora, o usuário deverá:

- Selecionar a operação desejada nas chaves SW(17..16).

- Fornecer um valor nas chaves SW(7..0) – operando A.

- Pressionar Enter – o botao KEY(1) será ‘0’ quando pressionado.

- Se a operação selecionada for de apenas um operando (divisão por 2 ou multiplicação por 2), o resultado será apresentado nos displays de 7-segmentos (hexadecimal), LEDs (binário), e LCD (decimal).

- Se a operação selecionada possuir dois operandos (soma ou subtração), fornecer o segundo operando nas chaves SW(7..0), pressionar Enter novamente, e o resultado será apresentado nos displays de 7-segmentos (hexadecimal), LEDs (binário), e LCD (decimal).

- Após apresentado o resultado, essa sequência é reiniciada, voltando ao passo 1.

- Simulador do LCD – usar esse simulador para verificar o comportamento do LCD de acordo com os comandos e dados enviados.

- Datasheet do LCD – informação detalhada sobre o LCD.

- Resumo dos comandos – Conjunto minimo de comandos para utilização do LCD.

- Display.c – Exemplo de programa em linguagem C para escrita no LCD.

Figura 1. Diagrama de blocos do circuito a ser desenvolvido em VHDL.

O circuito possui os seguintes componentes:

- Registrador – Esse componente foi desenvolvido inicialmente no Laboratório 6, e reutilizado nos demais laboratórios do semestre. Notar que são utilizados registradores de 4 e de 8 bits, e o circuito possui um total de quatro registradores. Cada registrador possui quatro entradas e uma saída:

- Clock – Entrada de 1 bit para conexão do sinal de relógio.

- D – Entrada de 4 ou 8 bits utilizada para receber o dado a ser armazenado. Sempre que o sinal de reset estiver em ‘0’ e o sinal de enable estiverem em ‘1’, e na ocorrência da borda de subida do clock, o valor na entrada D é armazenado no registrador;

- RST – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e faz com que o registrador seja inicializado com zero;

- EN – Entrada de 1 bit utilizada para habilitar (enable) a escrita (armazenamento) do dado de entrada (D). Essa entrada é ativa em nível lógico alto (‘1′);

- Q – Saída de 4 ou 8 bits utilizada para disponibilizar o dado armazenado.

- Operações aritméticas – Esses componentes foram desenvolvidos nas aulas de laboratório, com exceção do subtrator que deverá ser desenvolvido no projeto final.

- Multiplexador – Esse componente foi desenvolvido no Laboratório 4, e reutilizado nas demais aulas do semestre. No calculadora do projeto final são utilizados dois multiplexadores. O multiplexador desenvolvido no Laboratório 4 deve ser adaptado para utilização nas duas situações, ou seja, na multiplexação dos resultados das operações aritméticas (como na calculadora original), e no fornecimento dos dados a serem enviados para o LCD. Para isso, o multiplexador deverá ser adaptado para possuir um número maior de entradas. Dessa forma, o componente multiplexador deverá possuir os seguintes sinais:

- Seleção – Entrada de 5 bits, que no MUX1 é conectada a FSM de controle da calculadora, e no MUX2 é conectada a FSM de controle do LCD.

- Entradas de dados – Entradas de 8 bits, que no MUX1 recebem os resultados das operações realizadas pela calculadora, e no MUX2 recebem os dados e comandos a serem enviados para o LCD.

- Saída do mux – Sinal de 8 bits com a informação a ser enviada para o LCD (palavra de dado ou comando).

- FSM – O componente FSM implementa a máquina de estados responsável pelo controle das operações da calculadora. Esse componente poderá ser implementadoa diretamente a partir da FSM utilizada para o controle das operações da calculadora do Laboratório 9. No slide 16 é apresentado o diagrama de blocos da conexão da FSM ao bloco de dados (datapath) da calculadora. Notar nesse slide, que a FSM é responsável pela ativação dos sinais de Enable dos registradores da calculadora, assim como pela seleção da operação a ser realizada no MUX1. O componente FSM possui quatro sinais de entrada, e três sinais de saída:

- Clock – Entrada de 1 bit para conexão do sinal de relógio;

- Reset – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e força a FSM a ser posicionada em seu estado inicial;

- Enter – Entrada de 1 bit conectada ao botão KEY(1) da DE2. Essa entrada é utilizada pelo usuário para informar para a FSM que um novo operando foi fornecido nas chaves SW(7..0);

- Operation – Entrada de 2 bits conectada as chaves (17..16). Essa entrada é utilizada pelo usuário para informar a operação a ser realizada pela calculadora;

- Enable_1 – Saída de 1 bit utilizada pela FSM para armazenar um dos operandos no registrador de entrada.

- Enable_2 – Saída de 1 bit utilizada pela FSM para armazenar o resultado das operações nos três registradores de saída.

- Selection – Saída de 2 bits utilizada pela FSM para selecionar a operação a ser realizada pela calculadora, de acordo com o fornecido pelo usuário nas chaves SW(17..16).

- 7-seg decoder – Componente utilizado para converter os valores dos registradores de binário para sete segmentos. Esse componente pode ser aproveitado diretamente a partir do circuito desenvolvido originalmente no Laboratório 5. Esse componente possui uma entrada e uma saída:

- Entrada de 4 bits com o valor a ser convertido de binário para 7-segmentos;

- Saída de 7 bits contendo o valor convertido, pronto para acionamento dos displays de 7-segmentos.

- Bin2BCD – Conversor de binário para BCD. Esse componente é utilizado para a realizar a conversão de um valor binário de 8 bits, nos respectivos dígitos BCD. O valor máximo a ser representado em 8 bits é FFH, ou seja, 255 na base 10. Para esse valor máximo, o componente Bin2BCD deverá gerar na sua saída os dígitos 0010, 0101, e 0101, ou seja, 2 em binário, 5 em binário, e 5 em binário. Para o valor mínimo, ou seja 0H, os três dígitos BCD a serem gerados serão 0000, 0000, e 0000. Um possível algoritmo para realizar a implementação desse conversor está disponível no website do Prof. Haskell (link para cópia local). Notar que uma implementação inteiramente combinacional também é possível e, nesse caso, as entradas clock e reset descritas a seguir não seriam necessárias. Porém, essas entradas precisam aparecer obrigatoriamente na entity do componente, uma vez que fazem parte dessa especificação. Caso não sejam utilizadas, basta não conectá-las a nenhum sinal interno do componente. O circuito (topo) possui três desses componentes, sendo dois deles utilziados para a conversão de cada um dos operandos de entrada, e um outro utilziado para a conversão do resultado da operação realizada. Esse componente possui as seguintes entradas e saídas:

- Clock – Entrada de 1 bit para conexão do sinal de relógio;

- RST – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e pode ser utilizada para forçar uma possível implementação baseada em FSM a ser posicionada em seu estado inicial;

- D – Entrada de 8 bits contendo o valor em binário a ser convertido;

- U – Saída de 4 bits contendo um valor BCD (0 a 9) referente ao dígito menos significativo, ou seja, o dígito da unidade (Units) do valor de entrada;

- T – Saída de 4 bits contendo um valor BCD (0 a 9) referente ao dígito da dezena (Tens) do valor de entrada;

- H – Saída de 4 bits contendo um valor BCD (0 a 9) referente ao dígito mais significativo, ou seja, o dígito da centena (Hundreds) do valor de entrada.

- B2A – BCD to ASCII. Esse componente é utilizado para realizar a conversão de um dígito BCD de 4 bits para o respectivo valor da tabela ASCII de 8 bits. Esse componente é necessário, uma vez que o LCD apresenta na tela apenas caracteres da tabela ASCII. Serão necessários nove desses componentes no circuito, sendo um para cada dígito BCD convertido pelos componentes Bin2BCD. Como os valores a serem convertidos estão todos na faixa de 0 a 9 (códigos BCD), uma dica para realizar a conversão de uma forma bastante simples consiste na adição do valor 0011 na frente de cada dígito a ser convertido. Por exemplo, o dígito BCD 0001 seria convertido para 00110001, que na tabela ASCII se refere ao caractere ‘1’. Esse componente possui uma entrada e uma saída:

- D – Valor em BCD de 4 bits a ser convertido para ASCII;

- A – Valor convertido em ASCII da entrada recebida.

- 2-complement converter – Esse componente realiza a conversão de valores no formato complemento-2. Deve ser utilizado para apresentar valores negativos no LCD. Por exemplo, 11111111 representa o valor 255 em decimal. Porém, ao se considerar uma representação de números com sinal (complemento-2), 11111111 representará o valor -1 em decimal. Assim, para apresentar o valor -1 no LCD, será necessário converter 11111111 para 000000001, que será o valor a ser enviado para o conversor Bin2BCD. Além disso, o LCD controller (descrito a seguir), deverá saber que o número em questão é negativo, de forma a enviar o símbolo ‘-‘ para o LCD. Esse componente não foi conectado aos demais componentes da calculadora, e essa tarefa deverá ser realizada pelo projetista. Uma sugestão seria colocar esse componente conectado a entrada de um dos conversores Bin2BCD, e o flag de sinal poderia ser utilizado na entrada de seleção de um terceiro multiplexador (MUX3 a ser criado pelo projetista) para informar a um outro componente se o valor em questão é positivo ou negativo.

- LCD controller (FSM & counter) – Esse componente é responsável pelo envio de comandos e palavras de dados para o LCD. Dica: No Laboratório 8, no slide 12 é apresentado o diagrama de estados da FSM da calculadora, e antes da implementação da FSM do controlador do LCD, deverá ser projetado o diagrama de estados apropriado para a solução do problema. No slide 13 é apresentada uma sugestão de implementação em VHDL para a FSM do slide 12. Nessa implementação foram utilizados dois processos (process) para implementar a FSM, mas soluções com apenas um process (ver contador ASCII do Laboratório 7) também são aceitas. Esse componente deverá implementar a funcionalidade, também, de um contador, que é necessário para a geração do atraso utilizado para envio de dados e comandos para o LCD. A FSM a ser implementada deverá permanecer, continuamente, selecionando o MUX de forma a enviar para o LCD os caracteres a serem apresentados no display, ou palavras de comando para configurar a forma como o LCD irá trabalhar. O componente LCD controller possui quatro sinais de entrada, e três sinais de saída:

- Clock – Entrada de 1 bit para conexão do sinal de relógio;

- RST – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e força a FSM a ser posicionada em seu estado inicial;

- Operation – Entrada conectada as chaves SW(17..16), utilizada para receber a informação sobre qual a operação foi selecionada pelo usuário. Com essa informação a FSM irá decidir quais caracteres serão enviados para o LCD. Por exemplo, ao ser selecionada uma operação de soma, o LCD controller deverá enviar o caracter ‘+’ (2BH) para o LCD, como parte da string a ser apresentada no display.

- Sign – Entrada de 1 bit utilizada para informar para essa FSM qual o sinal (positivo ou negativo) do valor que está sendo enviado nesse momento para o LCD. Lembrando que existem três possibilidades de origem do dado a ser enviado para o LCD: resultado (saída do registrador de saída de 8 bits); operando 1 (saída do registrador de entrada de 8 bits); e operando 2 (chaves SW(7..0). Notar também que na entrada Sign existe uma interrogação. Logo, o projetista terá que definir as ligações e componentes necessários para obter o valor do sinal desejado. Por exemplo, pode ser necessário usar um Mux nessa entrada Sign, de forma a selecionar um dos três dados desejados.

- Select – Saída contendo a indentificação da entrada do MUX2 a ser selecionada;

- RS – Saída que será colocada em ‘0’ pelo componente, sempre que um comando (palavra de controle) for enviado para o LCD, ou ‘1’ quando for enviado um dado a ser apresentado no LCD;

- EN – Saída que será colocada em ‘1’, e depois em ‘0’ após um tempo mínimo de 500 ns, para escrever no LCD a informação presente na sua entrada (DATA).

- Ao alimentar o circuito (DE2) pela primeira vez, essa FSM deverá enviar para o LCD os três comandos 38H, 0FH, e 06H, colocando para isso a saída RS em ‘0’, e a saída EN em ‘1’ e depois em ‘0’, conforme apresentado a partir do slide 19 do Laboratório 2. Para enviar esses comandos para o LCD, a FSM deverá selecionar as entradas 10, 11 e 12 do MUX2, respectivamente. Após a etapa de configuração do LCD, os dados podem ser escritos no display, e a etapa de configuração não deve ser repetida.

- Colocar a saída RS em ‘1’, informando ao LCD que a partir desse momento serão enviados dados para o display, e não comandos.

- Enviar os três dígitos do primeiro operando para o LCD, iniciando pelo mais significativo. Se for uma operação de soma ou subtração (dois operandos), o primeiro operando estará nas entradas 4, 5 e 6 do MUX2 (fio de ligação verde da Figura 1). Se for uma multiplicação ou divisão (apenas um operando), o primeiro (e único) operando estará nas entradas 7, 8, e 9 do MUX2 (fio de ligação roxo da Figura 1).

- Enviar a operação a ser realizada para o LCD, que pode ser uma das operações existentes nas entradas 13, 14, 15, ou 16 do MUX2, dependendo da seleção realizada pelo usuário nas chaves SW(17..16), e presente na entrada Operation do MUX2.

- Enviar o segundo operando para o LCD. Se for uma operação de soma ou subtração (dois operandos), o segundo operando estará nas entradas 7, 8 e 9 do MUX2 (fio de ligação roxo da Figura 1). Se for uma multiplicação ou divisão (apenas um operando), o “segundo operando” a ser enviado para o LCD será o caractere ‘2’ (entrada 18 do MUX2).

- Enviar o sinal de igual para o LCD (entrada 17 do MUX2).

- Enviar os três dígitos da resposta da operação realizada para o LCD (entradas 1, 2 e 3 do MUX2).

- Enviar o comando de limpar o LCD (entrada 19 do MUX2), com a saída RS = ‘0’ (envio de palavra de controle para o LCD).

- Voltar para o passo 2, para iniciar uma nova escrita de dados no LCD.

- CLOCK_50 – Entrada de 1 bit conectada ao sinal de relógio de 50MHz da DE2;

- KEY(0) – Entrada de 1 bit representando o sinal de reset, ativo em nível lógico ‘0’;

- KEY(1) – Entrada de 1 bit representando o comando de Enter do usuário para entrada de operandos na calculadora;

- SW(17..16) – Operation, entrada de dados de 2 bits, onde o usuário informa a operação a ser realizada;

- SW(7..0) – Operands, entrada de dados de 8 bits, onde o usuário informa os operandos a serem utilizados na operação a ser realizada;

- HEX1 – Display de 7-segmentos. Saída de 7 bits utilizada para apresentação em hexadecimal da parte mais significativa do resultado da operação realizada;

- HEX0 – Display de 7-segmentos. Saída de 7 bits utilizada para apresentação em hexadecimal da parte menos significativa do resultado da operação realizada;

- LEDG(7..0) – LEDs verdes. Saída de 8 bits utilizada para apresentação nos LEDs verdes do resultado em binário da operação realizada.

- LEDR(3..0) – LEDs vermelhos. Saída de 4 bits utilizada para apresentar nos LEDs vermelhos os quatro flags de status da calculadora (Zero, Overflow, Carry, e Negativo);

- LCB_BLON – Saída de 1 bit que deverá ser mantida em nível lógico ‘1’ para ligar a backlight do LCD (o LCD da DE2 não possui luz de fundo);

- LCD_ON – Saída de 1 bit que deverá ser mantida em nível lógico ‘1’ para ligar o LCD;

- LCD_RW – Saída de 1 bit que deverá ser mantida em nível lógico ‘0’ para informar ao LCD que estarão sendo realizadas apenas operações de escrita no LCD;

- LCD_DATA – Saída de 8 bits onde deverá estar conectado o multiplexador responsável pelo envio de dados ao LCD (MUX2);

- LCD_RS – Saída de 1 bit onde está conectada a saída RS do componente LCD controller;

- LCD_EN – Saída de 1 bit onde está conectada a saída EN do componente LCD controller.

Exigências do projeto

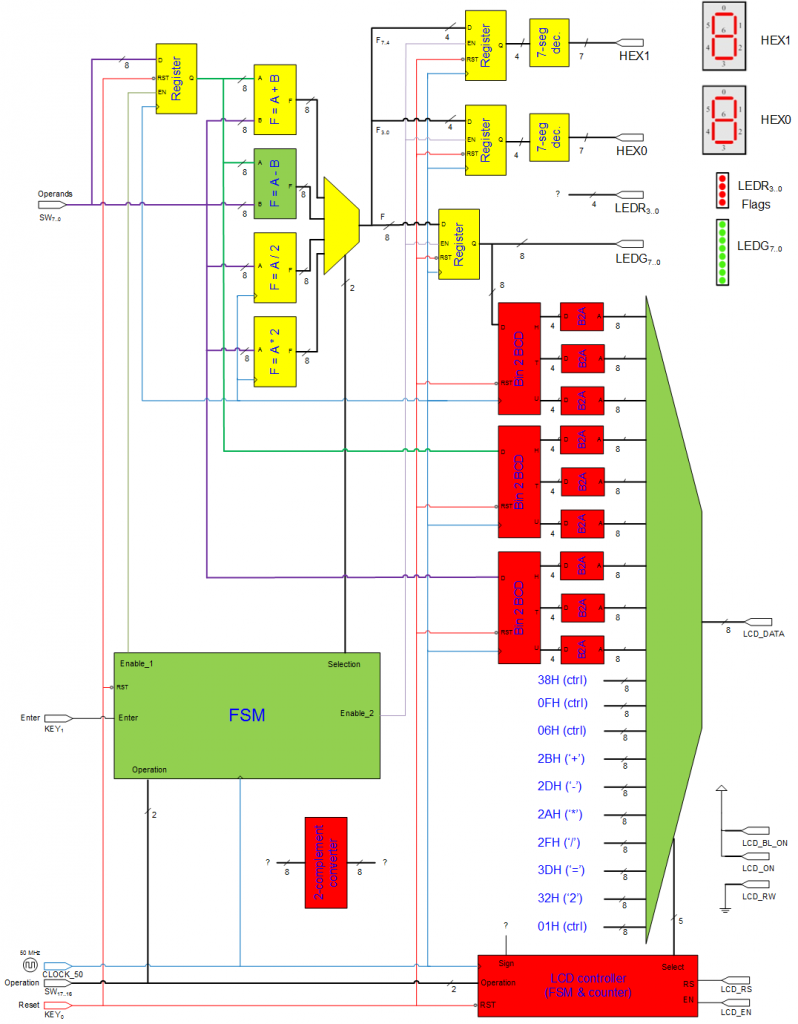

Figura 2. Diagrama de blocos destacando os componentes a serem reaproveitados, modificados e criados.

Teste e validação

Utilizar o simulador com formas de onda (Modelsim) para verificar o funcionamento do circuito, antes de testar na placa com FPGA.

Foi criado um script para automatizar o processo de criação da janela de formas de onda do Modelsim. Para utilizar o script, basta alterar o arquivo fornecido de acordo com os sinais a serem simulados no projeto em questão.

Algumas dicas:

- Utilizar o arquivo (script) compila.do como base.

- Esse script foi preparado para realizar a simulação do fonte VHDL teste.vhd, também disponível para download.

- O arquivo teste.vhd foi preparado para servir como exemplo de um fonte VHDL a ser simulado com o script compila.do, e a entity do teste.vhd possui alguns dos sinais esperados no topo do projeto final da disciplina.

- Para utilizar o script fornecido:

- Copiar o arquivo compila.do para a mesma pasta onde se encontra o projeto VHDL (arquivos a serem simulados)

- Editar o arquivo compila.do, e realizar as alterações necessárias, de acordo com seu projeto (alterar nomes de sinais, duração da simulação, valores dos sinais de entrada, sinais de clock, reset, …).

- No Quartus II, após realizar a síntese (compile), selecionar a opção para simulação conforme descrito no livro – RTL simulation

- Quando o Modelsim for executado, mudar para o diretório de trabalho onde se encontram os arquivos de projeto: Menu File -> Change directory – selecionar a pasta onde se encontra o projeto VHDL (arquivos a serem simulados e arquivo compila.do)

- Na linha de comando do Modelsim digitar o comando: do compila.do

- Ao ser executado, o script irá inicializar a simulação, criar a janela de formas de onda, colocar os sinais indicados na janela de forma de ondas, definir valores para os sinais, executar um passo de simulação, definir novos valores (force) para os sinais, realizar mais um passo de simulação, …

Documentação do projeto (relatório final)

- A documentação deverá ser completa e clara o suficiente para possibilitar alterações e atualizações na implementação do projeto, sem a necessidade de consultar os projetistas. Durante a correção da documentação o professor da disciplina irá realizar uma alteração no código VHDL, sem consultar os autores, com informações obtidas apenas a partir da documentação. Na avaliação final da documentação será considerado o grau de facilidade para realizar a alteração no VHDL.

- A documentação do projeto deverá conter uma descrição detalhada de todos os módulos desenvolvidos.

- O texto deverá DESCREVER o projeto, sem incluir a listagem completa do código VHDL implementado. Alguns trechos do código VHDL poderão ser incluídos na documentação, apenas quando necessário para alguma explicação de módulos implementados.

- Deverá ser incluído o fluxo completo do projeto, detalhando as ferramentas utilizadas e as etapas de projeto. A descrição do fluxo deve ser suficientemente detalhada de forma a facilitar a repetição de todas as etapas realizadas. No momento da correção do trabalho será consultada e seguida a descrição do fluxo de projeto existente na documentação. Dessa forma, descrições incompletas do fluxo de projeto poderão prejudicar a avaliação do trabalho.

- Preparar e incluir na documentação um diagrama de blocos completo com todos os módulos implementados. O diagrama de blocos deverá ser detalhado de forma a incluir todos os sinais de entrada e saída, e todos os módulos implementados.

- Deverá ser fornecida também a representação gráfica das máquinas de estados, tabelas de estados e explicações sobre estados e transições.

- Incluir os diagramas de forma de onda da simulação, com explicações sobre o que está acontecendo com os sinais nas formas de onda, mais exatamente, o que está sendo apresentado/observado na simulação/forma de onda em questão.

- Sugestão de organização para o documento do projeto:

- Folha de rosto contendo dados do autor, da instituição, local, data;

- Objetivos do trabalho;

- Especificação do problema proposto – visão/entendimento do autor sobre essa especificação;

- Projeto dos componentes do sistema com uma breve descrição do objetivo de cada componente. Incluir nessa descrição uma explicação (com diagrama de blocos e textual) dos componentes estudados na teoria e sua utilização na prática (ex. registradores, decodificadores, circuitos aritméticos, …);

- Descrição das ferramentas utilizadas e fluxo de projeto;

- Descrição da simulação realizada, com diagramas de forma de ondas extraídos diretamente do ModelSim;

- Considerações e conclusões sobre o trabalho realizado.

- É importante cuidar a coerência e a coesão da documentação, pois o documento entregue será essencial para o entendimento e correção do trabalho realizado.

- A documentação deverá ser entregue no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.

OBSERVAÇÃO IMPORTANTE!! O trabalho pode ser realizado em grupo, porém A AVALIAÇÃO É INDIVIDUAL. Cada integrante do grupo SERÁ QUESTIONADO INDIVIDUALMENTE, e deverá estar apto a UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULAÇÃO REALIZADA.

Código fonte VHDL e arquivo de projeto do Quartus II

- O código fonte VHDL deve estar adequadamente comentado – incluir um comentário explicativo em cada bloco de código e, sempre que necessário, em linhas individuais.

- Incluir um bloco de comentário no início do arquivo com o fonte VHDL contendo dados dos alunos e demais dados de identificação do projeto (ex. utilidade, ferramentas, FPGA alvo, …).

- O código fonte precisa estar com a indentação adequada.

- Escolher nomes adequados para os símbolos utilizados no programa (entities, architectures, signals, …).

- Os fontes VHDL deverão ser entregues no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.

- Gerar um arquivo compactado, contendo APENAS os fontes VHDL do projeto desenvolvido no Quartus II, e submeter apenas esse arquivo. O sistema de submissão de trabalhos disponível no Moodle aceitará a submissão de um único arquivo por grupo. Foi definido um tamanho máximo de arquivo que pode ser submetido, para garantir que o aluno irá enviar APENAS os fontes VHDL compactados em um único arquivo.

Etapas do projeto e dicas úteis

1. Dividir o problema em partes menores – abordagem “dividir para conquistar”:

- Desenvolver em VHDL e simular (diagrama de formas de onda) os componentes solicitados no trabalho. Durante o semestre, alguns desses circuitos foram desenvolvidos nas aulas teóricas e práticas como, por exemplo, registradores e máquinas de estados.

- Desenvolver e simular (diagrama de formas de onda) os circuitos combinacionais em VHDL para as operações lógicas e aritméticas a serem executadas.

- Seguir as dicas para implementação de circuitos controladores fornecidas nas aulas teóricas e práticas. Uma boa dica de descrição em VHDL de uma FSM de controlador é desenvolvida no Laboratório 8.

- Após ter certeza que todos os circuitos possuem o comportamento desejado, realizar a integração dos componentes desenvolvidos, formando gradualmente sistemas digitais mais completos que atendam aos requisitos fornecidos. A integração de componentes é realizada com port map, e foi apresentada e praticada desde o início do semestre a partir do Laboratório 3.

- Seguindo essa filosofia de projeto, poderia ser desenvolvida uma versão inicial do circuito com apenas uma funcionalidade e, após devidamente validada, as demais funcionalidades poderiam ser incluídas. Os componentes podem ser validados individualmente, antes de serem anexados ao projeto. Uma sugestão é comentar os port maps onde as conexões dos componentes são definidas, e ir removendo os comentários de forma a incluir os componentes gradualmente no circuito. As entradas dos componentes podem ser exercitadas por intermédio de chaves e botões, e as saídas podem ser observadas nos LEDs e LCD. Quando um componente é anexado ao circuito, essas entradas e saídas devem ser substituídas pelos sinais adequados da FSM de controle.

- ATENÇÃO!! Mesmo projetistas de sistemas digitais experientes, já atuando na indústria, não desenvolvem sistemas por inteiro sem antes simular e validar os componentes individualmente. Essa regra é seguida por projetistas experientes até para sistemas digitais considerados simples como, por exemplo, o projeto em questão.

2. Simulação do projeto:

- Utilizar ferramentas de simulação com formas de ondas, tais como, o ModelSim para simular os circuitos desenvolvidos individualmente.

- Realizar a simulação com os diagramas de formas de ondas dos diversos componentes desenvolvidos e, gradualmente, dos novos componentes compostos pela integração dos componentes menores, até chegar na implementação final do projeto.

- A simulação individual dos componentes é importante durante as etapas de desenvolvimento, mas apenas a simulação final com todos os componentes integrados (simulação do topo) pode ser considerada na validação final do projeto.

3. Prototipação na plataforma de desenvolvimento:

- Identificar os periféricos disponíveis no kit de desenvolvimento e pinos de entrada/saída, que poderão ser úteis no desenvolvimento do sistema digital solicitado.

- Testar na plataforma de desenvolvimento os diversos componentes conforme forem sendo desenvolvidos, assim como os componentes resultantes da integração dos módulos. Realizar os testes na plataforma de desenvolvimento, apenas após a simulação (diagramas de formas de onda) indicar que o sistema está funcionando de acordo com o esperado.

- As plataformas de desenvolvimento do laboratório não poderão ser emprestadas para os alunos, que deverão compartilhar as mesmas apenas no laboratório.

4. Ajuda:

- Procurar o monitor da disciplina e equipe de apoio para dúvidas sobre o projeto dos circuitos a serem utilizados.

Avaliação

- O trabalho poderá ser desenvolvido individualmente ou em grupos com, no máximo, três integrantes.

- O relatório é individual. Cada aluno da turma deverá preparar seu próprio relatório, expressando a sua opinião.

- O código VHDL pode ser o mesmo para todos os alunos de um mesmo grupo.

- Será avaliado, principalmente, o funcionamento de todos os componentes funcionando em conjunto, ou seja, a principal simulação a ser apresentada é a do arquivo “topo”. É preciso mostrar que a FSM está controlando adequadamente todos os demais componentes do circuito, com o mesmo clock sendo aplicado a todo o projeto (isso só é possível de ser observado no topo).

- A documentação do projeto e o fonte VHDL deverão ser entregues no Moodle:

- A entrega dos fontes VHDL e do relatório será realizada no Moodle.

- Não serão aceitos envios atrasados. O sistema do Moodle irá bloquear automaticamente após o prazo final da entrega.

- Em semestres anteriores, alunos que perderam o prazo para envio ficaram com nota zero no trabalho final.

- O sistema aceita vários envios (desde que dentro do prazo de entrega). Assim, é fortemente recomendado que todas as versões parciais do trabalho sejam enviadas no moodle (tanto o VHDL quanto o relatório).

- Uma nova submissão sobreescreve a anterior. Todos os alunos devem submeter pelo menos uma versão dos seus trabalhos por dia, garantindo que terá um trabalho para ser avaliado no final do semestre.

- O tamanho máximo do arquivo contendo o relatório é de 1 M bytes. Deverá ser submetido APENAS um arquivo, e esse arquivo deverá estar no formato PDF.

- O tamanho máximo do arquivo contendo os fontes VHDL é de 100 K bytes. Deverá ser submetido APENAS um arquivo compactado contendo todos os fontes VHDL.

- Não deverão ser incluídos arquivos de projeto do Quartus II no arquivo compactado – INCLUIR APENAS OS FONTES VHDL (.vhd).

- O nome do arquivo compactado com os fontes VHDL deverá ser o nome completo do aluno, sem espaçamento e sem acentuação. Por exemplo, o aluno “Eduardo Augusto Bezerra” deverá gerar o seguinte arquivo compactado com seus fontes VHDL: “EduardoAugustoBezerra.zip”

- TODOS OS ALUNOS DEVERÃO SUBMETER OS SEUS RELATÓRIOS E FONTES VHDL, MESMO QUE TENHAM DESENVOLVIDO OS TRABALHOS EM GRUPOS.

- O sistema de submissões de arquivos do Moodle é a ferramenta oficial para entrega de trabalhos da disciplina. NÃO SERÃO ACEITOS TRABALHOS ENVIADOS POR EMAIL, TRABALHOS IMPRESSOS, OU QUALQUER OUTRA FORMA DE ENTREGA A NÃO SER O SISTEMA DO MOODLE.

- A apresentação da simulação e a demonstração do funcionamento por intermédio de simulação será realizada nas semanas indicadas no cronograma das aulas. Os alunos deverão agendar a data e hora para apresentação do trabalho diretamente no Moodle, conforme instruções enviadas por email para todos os alunos.

- Durante a apresentação, os alunos deverão estar aptos a responder quaisquer perguntas. Respostas insatisfatórias ou a ausência do aluno poderá acarretar em anulação da nota final.

- Na apresentação serão realizados questionamentos sobre decisões de projeto e estratégias de implementação VHDL utilizadas. Será verificada também a familiaridade dos alunos com as ferramentas de desenvolvimento utilizadas durante o semestre. Todos os alunos devem estar aptos a responder todas as questões.

- As explicações durante a apresentação da documentação do projeto, e na demonstração do projeto funcionando por intermédio da simulação e dos diagramas de formas de onda, são fundamentais para a avaliação.

- Trabalhos copiados, inclusive entre turmas, resultarão em nota zero para todos os alunos envolvidos. Será utilizado o MOSS como ferramenta auxiliar na identificação de situações de plágio. Obviamente, similaridade de 100% nos fontes VHDL de um mesmo grupo é um resultado esperado. O mesmo não se espera em relação aos relatórios, que deverão ser diferentes mesmo entre integrantes do mesmo grupo.

- Os dois itens a serem avaliados possuem os seguintes pesos na nota final do trabalho prático:

- Documentação do projeto: 40%

- Demonstração do funcionamento por intermédio de simulação: 60%

OBSERVAÇÃO IMPORTANTE!! O trabalho poderá ser realizado em grupo, porém A AVALIAÇÃO É INDIVIDUAL. Cada integrante do grupo SERÁ QUESTIONADO INDIVIDUALMENTE, e deverá estar apto A UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULAÇÃO REALIZADA. Cada integrante do grupo deverá reservar um horário em separado para sua apresentação.