EEL-7020 – Sistemas Digitais

Definicao do Trabalho Pratico – 2011/2

“Projeto, implementacao e simulacao em VHDL/FPGA de um circuito para o calculo do consumo instantaneo de combustivel em um veiculo”

Departamento de Engenharia Eletrica,

CTC,

UFSC,

Florianopolis, SC, Brasil

1. Multiplicacao em binario – algoritmo soma e desloca:

- Um circuito para multiplicacao em binario aceita como entrada dois operandos de n bits cada um, fornecendo como saida um resultado de 2 * n bits. Por exemplo, considerando dois operandos de 8 bits cada um, o resultado da multiplicacao tera 16 bits.

- A Figura 1 apresenta os passos da multiplicacao em binario realizada manualmente. Nesse exemplo, os operandos (multiplicando e multiplicador) sao os valores 10 e 14 em decimal (primeira coluna). Assim, a operacao a ser realizada consiste em 10*14 = 140. A coluna DEC apresenta os passos para a multiplicacao em decimal. A coluna BIN apresenta os passos para a multiplicacao em binario. A terceira e ultima coluna, apresenta os resultados parciais das multiplicacıes em binario. A ultima linha apresenta o resultado final (produto) em decimal (primeira coluna) e binario (coluna do meio).

Figura 1. Exemplo de operacao de multiplicacao em decimal e em binario.

- Na Figura 2 e apresentado o diagrama de blocos de um circuito utilizado na execucao da multiplicacao de 4 bits descrita na Figura 1.

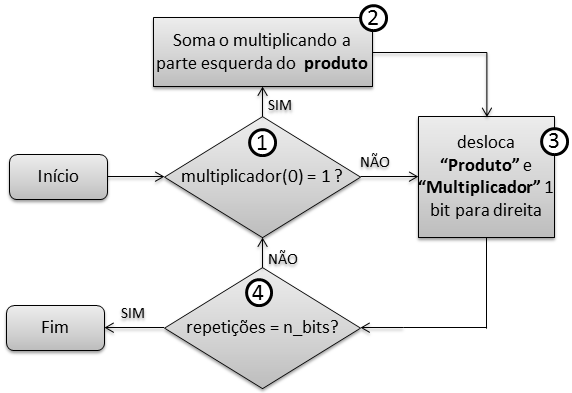

- A Figura 3 mostra o fluxograma do algoritmo de multiplicacao “soma e desloca” do circuito da Figura 2:

- Na Figura 2, o registrador “Multiplicando” de 4 bits e uma das entradas do somador (ULA), e a parte superior do registrador “Produto” (4 bits) e o segundo operando do somador.

- O “Multiplicador” esta armazenado na parte inferior (4 bits) do registrador “Produto”.

- Inicialmente, a parte superior do registrador “Produto” possui o valor zero (“0000″).

- O algoritmo inicia verificando se o bit 0 (menos significativo) do “Multiplicador” (localizado no registrador “Produto”), possui o valor ‘1’.

- Se o bit 0 do “Multiplicador” for igual a ‘1’, entao o “Multiplicando” e adicionado a parte superior do “Produto”.

- Se o bit 0 do “Multiplicador” for igual a ‘0’, entao o “Multiplicando” NAO e adicionado a parte superior do “Produto”.

- Em ambos os casos (Multiplicador(0) = ‘1’ ou ‘0’), o registrador “Produto” (incluindo o registrador embutido “Multiplicador”) e deslocado um bit a direita.

- O teste (Multiplicador(0) = ‘1’), seguido da soma do multiplicando com o produto, e do deslocamento do “Produto”, e repetido 4 vezes (n vezes), que e o tamanho do “Multiplicando” e do “Multiplicador”.

- Apos as n repeticoes (4, no exemplo em questao), o registrador “Produto” armazenara o resultado da multiplicacao.

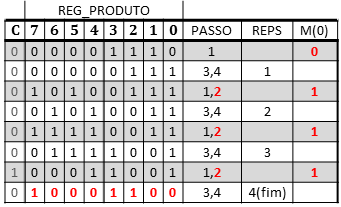

- A Figura 4 mostra o conteudo do registrador “Produto” a cada passo do algoritmo.

Figura 2. Diagrama de blocos de circuito para multiplicacao de operandos de 4 bits.

Figura 3. Fluxograma do algoritmo de multiplicacao “soma e desloca” de um multiplicador de n bits.

Figura 4. Conteudo do “registrador de produto” a cada etapa de execucao do algoritmo de multiplicacao “soma e desloca” de um multiplicador de 4 bits.

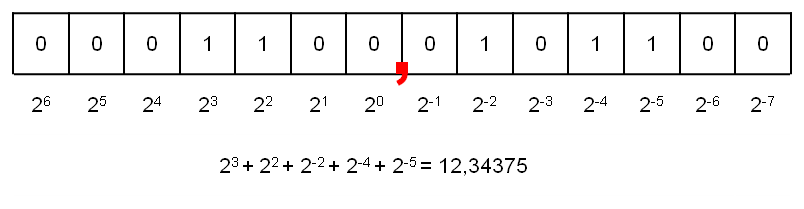

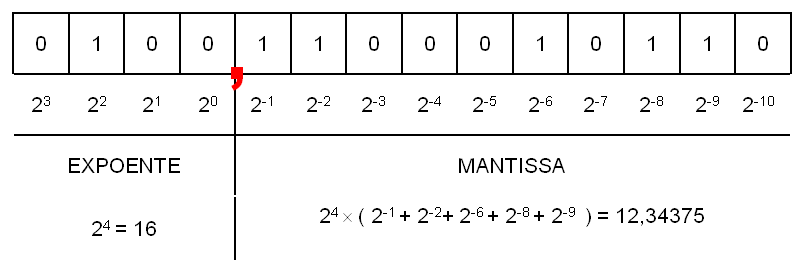

2. Representacao de numeros com virgula em binario

- Ponto Fixo

- Ponto Flutuante

- Ponto Flutuante Polarizado (NAO sera utilizado nesse trabalho)

- Sistemas que utilizam o padrao IEEE-754 usam a “polarizacao” para armazenar o valor do expoente. A polarizacao facilita a comparacao dos expoentes no nivel logico.

- A representacao com polarizacao NAO sera utilizada nesse trabalho.

- Sistemas que utilizam o padrao IEEE-754 usam a “polarizacao” para armazenar o valor do expoente. A polarizacao facilita a comparacao dos expoentes no nivel logico.

- Normalizacao

- A “normalizacao” e utilizada para padronizar a representacao dos numeros e, tambem, para facilitar as operacıes aritmeticas.

Neste trabalho, um numero binario sera considerado normalizado quando o bit mais significativo MSB da mantissa for UM.

Se o numero estiver normalizado, e o MSB for ZERO, entao isso significa que se trata da representacao em ponto flutuante do valor ZERO.

0,d1d2d3…* 2e onde d1 = 1 - Exemplos de numeros normalizados:

- 1111 11111111 = (255/256) * 215 = 255 * 27 [Maior numero representavel]

- 0000 10000000 = (128/256) * 20 = 0,5 [Menor numero normalizado]

- 0001 10000000 = (128/256) * 21 = 1 [Mantissa = 10000000, expoente = 1]

- 0101 10001000 = (136/256) * 25 = 17 [Mantissa = 10001000, expoente = 5]

- 11,125 = 1011,001 = 0,1011001 * 24 [Mantissa = 1011001, expoente = 4]

- 2,3125 = 10,0101 = 0,100101 * 22 [Mantissa = 100101, expoente = 2]

- 0,375 = 0,011 = 0,11 * 2-1 [Mantissa = 11000000, expoente = -1]

- 0,000 = 0 * 20 = zero [Mantissa = 00000000, expoente = 0]

- Exemplos de numeros NAO normalizados:

- 11,125 = 1011,001 = 0,01011001 * 25 [Mantissa = 01011001, expoente = 5]

- 2,3125 = 10,0101 = 0,00100101 * 24 [Mantissa = 00100101, expoente = 4]

- 0,375 = 0,011 = 0,011 * 20 [Mantissa = 011, expoente = 0]

- 0,000 * 213 = zero? [Mantissa = 0, expoente = 13]

- A “normalizacao” e utilizada para padronizar a representacao dos numeros e, tambem, para facilitar as operacıes aritmeticas.

- Solucoes em software de aritmetica de ponto flutuante sao mais lentas do que solucıes em hardware (aproximadamente 1.000 vezes mais lentas). Por essa razao, circuitos para multiplicacao em ponto flutuante sao largamente utilizados em uma variedade de aplicacoes.

- O calculo do consumo instantaneo de combustivel, realizado pelo computador de bordo de um determinado veiculo, e um bom exemplo de aplicacao que necessita velocidade de processamento ao lidar com numeros em ponto flutuante.

Para calcular o consumo instantaneo de combustivel sao utilizado dados provenientes de diversos sensores do veiculo. E’ preciso obter a taxa de injecao de combustivel, a rotacao do motor, a distancia percorrida, a velocidade, entre outros.

Assim, diversos sensores sao lidos e calculos sao realizados muitas vezes por segundo, de forma a manter o motorista constantemente atualizado sobre o consumo instantaneo do seu veiculo.

Para facilitar a implementacao do circuito, assumir que o consumo instantaneo de combustivel e calculado pela seguinte equacao:

- A distancia percorrida e a quantidade de combustivel injetado sao valores binarios em ponto flutuante, calculados por um circuito dedicado, a partir de dados recebidos de sensores.

- Projetar e implementar em VHDL um circuito para o calculo do consumo instantaneo de combustivel, que utiliza como entrada as duas informacoes da equacao anterior.

Trata-se de um circuito para multiplicacao em ponto flutuante, que devera ser implementado em VHDL conforme o diagrama de blocos apresentado na Figura 7.

Figura 7. Diagrama de blocos do circuito a ser implementado em VHDL. - O formato dos operandos e do resultado fornecido pelo circuito esta representado na Figura 8. Nesse formato, cada valor possui 12 bits, sendo 4 bits para o expoente e 8 bits para a mantissa.

Figura 8. Formato dos operandos e resultado. - Conforme apresentado na Figura 7, o circuito possui um total de 10 sinais (bits) de entrada, e 13 sinais (bits) de saida.

- Os 10 bits de entrada sao fornecidos por 8 chaves, SW(7 downto 0), e por dois push-buttons, KEY(0) e KEY(1), onde:

- O push-button KEY(0) devera ser utilizado para realizar a inicializacao (reset) do circuito.

- O push-button KEY(1) devera ser utilizado para alimentar o circuito com as “partes” dos operandos fornecidos por intermedio das chaves SW(7 downto 0).

- Os 13 bits de saida sao apresentados ao usuario por intermedio dos LEDs vermelhos e verdes, onde:

- Os 4 bits do expoente sao apresentados nos LEDs vermelhos LEDR(3 downto 0).

- Os 8 bits da mantissa sao apresentados nos LEDs verdes LEDG(7 downto 0).

- A ocorrÍncia de overflow devera ser indicada em um LED verde – LEDG(8).

- A carga dos operandos de entrada no circuito deve ser comandada pelo push-button KEY(1) da seguinte forma:

- Ao se pressionar KEY(1) pela primeira vez, os 8 bits da mantissa do primeiro operando sao obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Ao se pressionar KEY(1) pela segunda vez, os 8 bits da mantissa do segundo operando sao obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Ao se pressionar KEY(1) pela terceira vez, os dois expoentes de 4 bits de ambos operandos sao obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Apos KEY(1) ter sido pressionado pela terceira vez, todos os operandos foram carregados, e o circuito realiza a multiplicacao em ponto flutuante automaticamente, fornecendo o resultado nos LEDs vermelhos e verdes.

- Todo o controle da entrada de dados, execucao da multiplicacao em ponto flutuante, e apresentacao dos resultados, deve ser realizado pela maquina de estados implementada no bloco CONTROLE da Figura 7.

- Se o resultado a ser apresentado na saida (LEDs vermelhos e verdes) for diferente de zero, entao este devera estar normalizado, mesmo que os operandos de entrada nao estejam normalizados.

- Para realizar a normalizacao, sera necessario deslocar a mantissa ate que o primeiro digito apos a virgula seja ‘1’. … preciso contar o numero total de deslocamentos realizados, e alterar o expoente de acordo. Isso deve ser realizado pelo modulo “Contador de 5 bits” da Figura 7.

- Assumir que nunca ira ocorrer underflow de expoentes.

- A ocorrÍncia de overflow devera ser indicada em um LED verde – LEDG(8).

- Material de apoio para o desenvolvimento do trabalho:

- A documentacao devera ser completa e clara o suficiente para possibilitar

alteracıes e atualizacıes na implementacao do projeto, sem a necessidade de consultar os

projetistas. Durante a correcao da documentacao o professor da disciplina ira realizar uma

alteracao no codigo VHDL, sem consultar os autores, com informacıes obtidas apenas a partir

da documentacao. Na avaliacao final da documentacao sera considerado o grau de facilidade

para realizar a alteracao no VHDL. - A documentacao do projeto devera conter uma descricao detalhada de todos os modulos desenvolvidos.

- O texto devera DESCREVER o projeto, sem incluir a listagem completa do codigo VHDL implementado.

Alguns trechos do codigo VHDL poderao ser incluidos na documentacao, apenas quando necessario

para alguma explicacao de modulos implementados. - Devera ser incluido o fluxo completo do projeto, detalhando as ferramentas utilizadas e as

etapas de projeto. A descricao do fluxo deve ser suficientemente detalhada de forma a

facilitar a repeticao de todas as etapas realizadas. No momento da correcao do trabalho

sera consultada e seguida a descricao do fluxo de projeto existente na documentacao. Dessa

forma, descricıes incompletas do fluxo de projeto poderao prejudicar a avaliacao do trabalho. - Preparar e incluir na documentacao um diagrama de blocos completo com todos os modulos implementados.

O diagrama de blocos devera ser detalhado de forma a incluir todos os sinais de entrada e saida,

e todos os modulos implementados. - Devera ser fornecida tambem a representacao grafica das maquinas de estados, tabelas de estados e

explicacıes sobre estados e transicıes. - Sugestao de organizacao para o documento do projeto:

- Folha de rosto contendo dados do autor, da instituicao, local, data;

- Objetivos do trabalho;

- Especificacao do problema proposto – visao/entendimento do autor sobre essa especificacao;

- Projeto dos componentes do sistema com uma breve descricao do objetivo de cada componente.

Incluir nessa descricao uma explicacao (com diagrama de blocos e textual) dos componentes

estudados na teoria e sua utilizacao na pratica (ex. multiplexadores, decodificadores, circuitos

aritmeticos, …); - Descricao das ferramentas utilizadas e fluxo de projeto;

- Descricao da simulacao realizada, com diagramas de forma de ondas extraidos diretamente do Quartus II ou ModelSim;

- Consideracıes e conclusıes sobre o trabalho realizado.

- … importante cuidar a coerÍncia e a coesao da documentacao, pois o documento entregue sera

essencial para o entendimento e correcao do trabalho realizado. - A documentacao devera ser entregue no Moodle,

obedecendo RIGOROSAMENTE o prazo estipulado.

- O codigo fonte VHDL deve estar adequadamente comentado – incluir um comentario explicativo em cada

bloco de codigo e, sempre que necessario, em linhas individuais. - Incluir um bloco de comentario no inicio do arquivo com o fonte VHDL contendo

dados dos alunos e demais dados de identificacao do projeto (ex. utilidade, ferramentas, FPGA alvo, …). - O codigo fonte precisa estar com a indentacao adequada.

- Escolher nomes adequados para os simbolos utilizados no programa (entities, architectures, signals, …).

- Os fontes VHDL deverao ser entregues no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.

- Gerar um arquivo compactado, contendo APENAS os fontes VHDL do projeto desenvolvido no Quartus II, e submeter apenas esse arquivo. O sistema de submissao de trabalhos disponivel no Moodle aceitara a submissao de um unico arquivo por grupo.

- Desenvolver circuitos em VHDL para acesso aos perifericos da placa com o FPGA. Durante o semestre,

alguns desses circuitos foram desenvolvidos nas aulas teoricas e praticas como, por exemplo, registradores e maquinas de estados. - Desenvolver circuitos combinacionais em VHDL para as operacıes logicas e aritmeticas a serem executadas.

- Seguir as dicas para implementacao de circuitos controladores fornecidas

nas aulas teoricas e praticas. Uma boa dica de descricao em VHDL de uma FSM de controlador

e desenvolvida no Laboratorio 9. - Apos ter certeza que todos os circuitos possuem o comportamento desejado, realizar a integracao dos

componentes desenvolvidos, formando gradualmente sistemas digitais mais completos que atendam aos

requisitos fornecidos. A integracao de componentes e discutida no Lab 6 (port map). - Seguindo essa filosofia de projeto, poderia ser desenvolvida uma versao inicial do projeto com apenas uma

funcionalidade, por exemplo, e apos devidamente validada, as demais funcionalidades poderiam

ser incluidas (todos os novos componentes sendo validados individualmente, antes de serem

anexados ao projeto). - ATEN«√O!! Mesmo projetistas de sistemas digitais experientes, ja atuando na

industria, nao desenvolvem sistemas por inteiro sem antes simular e validar os componentes

individualmente. Essa regra e seguida por projetistas experientes ate para sistemas digitais

considerados simples como, por exemplo, o projeto em questao.

2. Simulacao do projeto:

- Utilizar ferramentas de simulacao com formas de ondas, tais como, o ModelSim ou o Quartus II para simular os circuitos

desenvolvidos individualmente. - Realizar a simulacao com os diagramas de formas de ondas dos diversos componentes desenvolvidos e,

gradualmente, dos novos componentes compostos pela integracao dos componentes menores, ate chegar

na implementacao final do projeto.

3. Prototipacao no kit com FPGA:

- Identificar os perifericos disponiveis no kit de desenvolvimento e pinos de entrada/saida, que poderao ser uteis

no desenvolvimento do sistema digital solicitado. Informacıes sobre pinos e perifericos poderao ser

encontradas no Manual do Usuario da Placa DE2, ou

no manual do usuario de algum outro kit selecionado para o projeto. - Testar no FPGA os diversos componentes conforme forem sendo desenvolvidos, assim como os componentes

resultantes da integracao dos modulos. Realizar os testes na placa, apenas apos a simulacao indicar

que o sistema esta funcionando de acordo com o esperado. - Os kits de ensino do laboratorio nao poderao ser emprestados para os alunos, que deverao compartilhar os mesmos apenas no

laboratorio.

4. Ajuda:

- Procurar o monitor da disciplina para duvidas sobre o projeto dos circuitos a serem utilizados.

- Verificar as agendas semanais dos professores da disciplina para agendar horarios de atendimento e, tambem,

para agendar a data/hora da apresentacao do trabalho que devera ser realizada na semana que inicia no dia 28 de novembro:

- O trabalho podera ser desenvolvido individualmente ou em grupos com, no maximo, tres integrantes.

- A documentacao do projeto e o fonte VHDL deverao ser entregues no Moodle no dia 25 de novembro de 2011.

- A apresentacao da simulacao e a demonstracao do funcionamento por intermedio de simulacao sera realizada

na semana de 28 de novembro a 02 de dezembro 2011. O grupo devera agendar

a data e hora para apresentacao do trabalho durante essa semana. - Durante a apresentacao, os alunos deverao estar aptos a responder quaisquer perguntas. Respostas

insatisfatorias ou a ausÍncia dos alunos podera acarretar em anulacao da nota final. - Na apresentacao serao realizados questionamentos sobre decisıes de projeto e estrategias

de implementacao VHDL utilizadas. Sera verificada tambem a familiaridade dos alunos com

as ferramentas de desenvolvimento utilizadas durante o semestre. Todos os alunos do grupo

devem estar aptos a responder todas as questıes. - As explicacoes durante a apresentacao da documentacao do projeto, e na demonstracao do projeto

funcionando por intermedio da simulacao e dos diagramas de formas de onda, sao fundamentais

para a avaliacao. - Trabalhos copiados, inclusive entre turmas, resultarao em nota zero para todos os alunos envolvidos.

Sera utilizado o MOSS como ferramenta auxiliar

na identificacao de situacıes de plagio. - Os dois itens a serem avaliados possuem os seguintes pesos na nota final do trabalho pratico:

- Documentacao do projeto: 50%

- Demonstracao do funcionamento por intermedio de simulacao no Quartus II ou ModelSim: 50%

- OBSERVACAO IMPORTANTE!! O trabalho podera ser realizado em grupo, porem A AVALIACAO E’ INDIVIDUAL. Cada integrante do grupo SERA’ QUESTIONADO

INDIVIDUALMENTE, e devera estar apto A UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULACAO REALIZADA.