“Frequencímetro Digital com Ponto Flutuante”

UFSC/CTC/EEL, semestre 2013/1

EEL7020 – Sistemas Digitais

Prof. Eduardo Augusto Bezerra

Prof. Joni da Silva Fraga

Prof. Djones Vinicius Lettnin

Descrição Geral do Problema

O projeto final consiste na implementação em VHDL para FPGAs de um circuito digital que realize a medida de uma frequencia de entrada e apresente o valor lido em displays de sete segmentos.

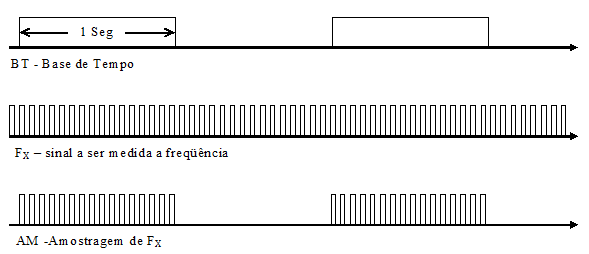

O frequencimetro é um instrumento utilizado para medir a quantidade de pulsos em um segundo (Hz), ou seja, a frequência de um sinal periódico. Esta contagem de pulsos por segundo é feita através da amostragem do sinal a ser medido, usando outro sinal normalmente chamado de “Base de Tempo”, de duração de um segundo. A Figura 1 ilustra o sinal a ser medido a frequência (Fx), o sinal Base de Tempo (BT) e o sinal amostrado (AM).

Figura 1. Amostras do sinal Fx a serem contadas.

Figura 1. Amostras do sinal Fx a serem contadas.

Para realizar a amostragem do sinal a ser medido, o frequencimetro utiliza um sinal de relógio (clock) de referência, e circuitos contadores. A proposta deste projeto é a construção de um frequencímetro em ponto flutuante que possa medir sinais com frequência até 10MHZ.

Especificação

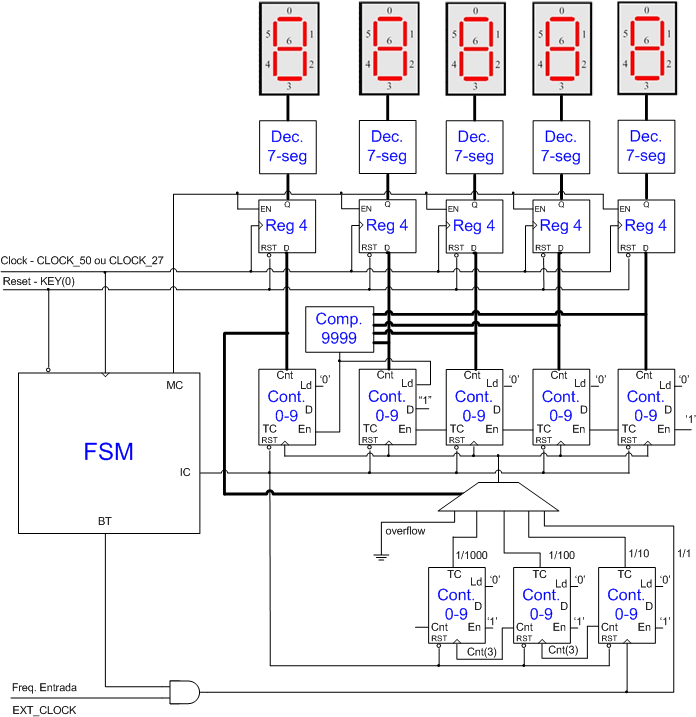

Na Figura 2 está apresentado o diagrama de blocos do circuito a ser implementado. Para utilizar o frequencímetro, o usuário deverá conectar um gerador de funções na entrada “Frequencia de entrada”, e pressionar o botão de reset key(0). Após isso, o frequencímetro irá apresentar a mantissa do valor medido nos quatro displays de sete segmentos do canto superior direito da Figura 2. No display mais a esquerda é apresentado o expoente da grandeza medida. Esses expoentes serão usados na base 10, e os possíveis valores são 0, 1, 2, 3, e 4. O valor 4 indicará overflow do instrumento. Assim, considerando os quatro digitos da mantissa, e o expoente máximo com valor 3, a maior frequencia medida pelo circuito será de 10 MHz (9999 x 10^3 pulsos por segundo).

O instrumento então será composto por cinco escalas que serão selecionadas automaticamente, se adaptando a frequência a ser medida. Estas escalas são então caracterizadas por medirem frequências com valores específicos:

- Escala 0 : frequências entre 0000 x 100 e 9999 x100 Hz

- Escala 1 : frequências entre 1000 x 101 e 9999 x101 Hz

- Escala 2 : frequências entre 1000 x 102 e 9999 x102 Hz

- Escala 3 : frequências entre 1000 x 103 e 9999 x103 Hz

Figura 2. Diagrama de blocos do circuito a ser desenvolvido em VHDL.

O circuito possui os seguintes componentes:

- Registrador – Esse componente foi desenvolvido inicialmente no Laboratório 6, e reutilizado nos demais laboratórios do semestre. Notar que o registrador a ser utilizado possui 4 bits, e o circuito possui um total de cinco registradores. Cada registrador possui quatro entradas e uma saída:

- Clock – Entrada de 1 bit para conexão do sinal de relógio.

- D – Entrada de 4 bits utilizada para receber o dado a ser armazenado. Sempre que os sinais de reset e enable estiverem em ‘1’, e na ocorrência da borda de subida do clock, o valor na entrada D é armazenado no registrador;

- RST – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e faz com que o registrador seja inicializado com zero (“0000″);

- EN – Entrada de 1 bit utilizada para habilitar (enable) a escrita (armazenamento) do dado de entrada (D). Essa entrada é ativa em nível lógico alto (‘1′);

- Q – Saída de 4 bits utilizada para disponibilizar o dado armazenado.

- Contador – Esse componente realiza uma contagem BCD, sequencial, de 0 a 9, fornecendo na sua saída Cnt os valores dessa contagem. Esse componente poderá ser adaptado a partir do Contador ASCII desenvolvido no Laboratório 7. As principais alterações devem ser os valores de início e fim de contagem, que no contador ASCII eram 41H e 5AH, respectivamente, e também a remoção dos estados utilizados para a geração do atraso de 1 segundo, uma vez que no projeto final o contador será incrementado sempre que ocorrer uma transição de 0 para 1 na sua entrada “clock”. Ao atingir a contagem máxima, ou seja, 9, a saída TC (Término de Contagem) apresentará o valor 1. No próximo pulso de clock o contador voltará para o valor inicial “0000”, e o TC também voltará para ‘0’. Os vários contadores do projeto deverão ser instanciados por intermédio de “port maps” a partir de um mesmo componente Contador BCD. Os contadores usados na contagem da frequência Fx (sinal a ser medido) deverão estar conectados nas entradas D dos registradores, disponibilizando assim os valores para apresentação nos displays de 7-segmentos. A frequência de entrada Fx deverá passar por um processo de divisões por dez para se adaptar as diferentes escalas do instrumento e os contadores BCD serão também usados neste processo de divisão. Serão, portanto, usadas oito cópias do contador BCD neste projeto. Cada componente contador possui cinco entradas e duas saídas:

- Clock – Entrada de 1 bit para conexão do sinal de relógio;

- RST – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e faz com que o contador seja inicializado com zero (“0000);

- En – Entrada de 1 bit utilizada para habilitar (enable) a contagem. Sempre que essa entrada e o reset estiverem em nível lógico alto (‘1′), e na ocorrência de um pulso de clock (borda de subida ou descida, de acordo com a decisão de projeto), o contador será incrementado uma unidade;

- D – Entrada de 4 bits utilizada para receber um valor de inicialização para o contador. Sempre que o sinal Ld (load) estiver em ‘1’, o valor presente na entrada D será armazenado no contador para ser utilizado como o valor inicial da contagem a ser realizada;

- Ld – Load. Entrada de 1 bit utilizada para carregar no contador o valor de início de contagem presente na entrada D;

- TC – Término de Contagem. Saída de 1 bit utilizada para indicar que o contador atingiu seu valor máximo de contagem. No caso desse contador, sempre que a contagem atingir o valor 9, a saída TC será ‘1’. Para todos os demais valores de contagem, a saída TC será ‘0’;

- Cnt – Saída de 4 bits que contém o valor atual da contagem.

- Seleção (Mux) – Esse componente foi desenvolvido no Laboratório 4, e reutilizado nas demais aulas do semestre. No circuito proposto, o sinal de entrada Fx deverá passar por um processo de divisões sucessivas para se adequar as diferentes escalas do instrumento. A seleção da frequência a ser contada é feita com um Mux entre suas diferentes entradas (Fx, Fx/10, Fx/100, Fx/1000). A entrada de seleção do Mux corresponde às saídas do contador de expoente. Este contador determina a escala a ser usada pelo instrumento. Durante a contagem (com BT=1 seg) quando os contadores de mantissa atingirem o valor máximo da escala (9999), estes habilitam o incremento do contador de expoente, e no próximo pulso da frequência medida, será utilizada uma escala superior. Na ocorrência de uma mudança de escala os contadores da mantissa iniciam novamente. Para não perder a contagem da escala anterior, o contador mais significativo da mantissa deve iniciar com o valor “1” (ou seja, o valor que segue o maior valor da escala anterior). Assim, o contador deverá possuir uma entrada de carga (load), ou seja, deverá ser implementado um “contador de carga paralela”. O multiplexador possui seis entradas e 1uma saída:

- Seleção – Entrada de 3 bits conectada diretamente a saída Cnt, que possui o valor da contagem do expoente. Assim, quando o expoente for 0, o sinal de entrada (frequencia a ser medida) é enviado diretamente para a saída do mux. Quando o expoente for 1, será selecionada a entrada do mux onde se encontra a saída do contador reponsável pela divisão da frequencia de entrada por 10. O funcionamento das entradas 2 e 3 do mux é semelhante ao funcionamento da entrada 1. Quando o expoente for 4, indicando overflow, será selecionada a entrada 4 do mux, que possui o valor zero (‘0′).

- Entradas 0 a 4 – Entradas de 1 bit, que recebem os respectivos sinais da frequencia sendo amostrada.

- Saída do mux – Sinal de 1 bit que representa a frequencia a ser utilizada para incrementar os contadores dos dígitos da mantissa e do expoente.

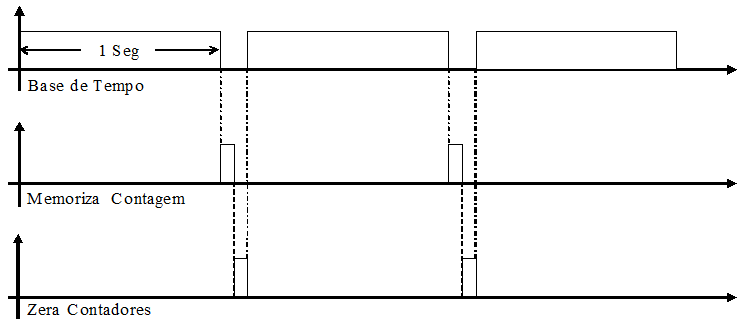

- FSM – O componente FSM implementa a máquina de estados responsável pelo controle das atividades do frequencímetro. Essa FSM poderá ser desenvolvida a partir da FSM utilizada para o controle das operações da calculadora do Laboratório 8. No slide 10 é apresentado o diagrama de blocos da conexão da FSM ao bloco de dados (datapath) da calculadora. Notar nesse slide, que a FSM é responsável pela ativação dos sinais de Enable dos registradores da calculadora, de forma bastante semelhante ao que deverá ser realizado pela FSM de controle do projeto do frequencímetro. A FSM do frequencímetro deverá gerar o sinal de saida “BT – Base de Tempo” (pulso de 1 segundo que permite a contagem da frequência a ser medida). No fim da saída Base de Tempo, deve ser gerado outro sinal de saída que é o “MC – Memoriza Contagem” que habilita a memorização dos valores de contagem nos registradores de saída do frequencímetro. Por fim a FSM, depois da memorização dos valores contados, deve gerar outra saída que é a “IC – Inicializa Contadores” para começar uma nova contagem na próxima Base de Tempo. A Figura 3 mostra a relação destes três sinais de saída da FSM. Sugestão: a FMS pode gerar o sinal da base de tempo de 1 segundo em nível alto em dez pulsos do clock que alimenta a FSM. Com isto, a frequência da FSM deve ser de 10 Hz. Para se conseguir esta frequência de 10 Hz pode se usar um dos dois sinais de clock disponíveis na placa do FPGA Altera que são 50MHz ou 27MHz. Ou seja, um desses dois sinais de clock deve ser dividido para gerar os 10Hz. Dica: No Laboratório 8, no slide 12 é apresentado o diagrama de estados da FSM da calculadora, e antes da implementação da FSM do frequencímetro, deverá ser projetado o diagrama de estados apropriado para a solução do problema. No slide 13 é apresentada uma sugestão de implementação em VHDL para a FSM do slide 12. Nessa implementação foram utilizados dois processos (process) para implementar a FSM, mas soluções com apenas um process (ver contador ASCII do Laboratório 7) também são aceitas. O componente FSM possui dois sinais de entrada, e três sinais de saída:

- Clock – Entrada de 1 bit para conexão do sinal de relógio;

- Reset – Entrada de 1 bit utilizada para receber o sinal de reset do sistema. Essa entrada é ativa em nível lógico baixo (‘0′), e força a FSM a ser posicionada em seu estado inicial;

- BT – Base de Tempo – Saída de 1 bit utilizada pela FSM para gerar um pulso de 1 segundo. Esse é o tempo de amostragem do sinal de entrada (frequencia a ser medida);

- MC – Memoriza Contagem – Saída de 1 bit utilizada pela FSM para habilitar os registradores para armazenar o valor da mantissa e expoente, que representam a frequencia medida pelo frequencimento;

- IC – Inicializa Contadores – Saída de 1 bit utilizada pela FSM para realizar um reset em todos os 8 contadores do circuito, colocando todos em zero e inicializando a mantissa, expoente, e divisores de frequencia.

- Decodificador de binário para 7-segmentos – Componente utilizado para converter os valores dos registradores de binário para sete segmentos. Esse componente pode ser adaptado a partir do circuito desenvolvido originalmente no Laboratório 5. Esse componente possui uma entrada e uma saída:

- Entrada de 4 bits com o valor a ser convertido de binário para 7-segmentos;

- Saída de 7 bits contendo o valor convertido, pronto para acionamento dos displays de 7-segmentos.

- Comparador – Esse componente realiza uma comparação entre suas entradas, e quando todas forem iguais a 9 (em decimal) então um sinal ‘1’ é fornecido na sua saída. Caso contrário, um sinal ‘0’ é fornecido na sua saída. Alternativamente, pode ser utilizada uma porta AND de 4 entradas, onde cada entrada possui um bit vindo diretamente das saídas TC de cada um dos quatro contadores de mantissa. O compoente comparador possui quatro entradas e uma saída:

- Quatro entradas de 4 bits cada uma (ou de 1 bit), que são conectadas diretamente às saídas dos contadores que representam a mantissa. Quando os quatro dígitos da mantissa são iguais a 9, isso significa que o fundo da escala foi alcançado, e o expoente deve ser incrementado.

- Uma saída de 1 bit. Essa saída é conectada à entrada Enable do contador de expoente, e quando for igual a ‘1’, isso significa que o valor máximo da escala atual foi alcançado, e o contador de expoente deve ser incrementado possibilitando que o frequencímetro mude automaticamente para a próxima escala (ou indique overflow, se for o caso). Além disso, essa saída também é conectada à entrada Ld (load) do contador, que representa o dígito mais significativo da mantissa, fazendo com que esse dígito seja carregado (inicializado) com o valor 1 em decimal, garantindo assim a memorização do valor de início da próxima escala (ver as escalas definidas para o frequencímetro logo acima da Figura 2).

- O clock é um sinal de entrada de 1 bit, e pode ser o sinal CLOCK_50 (50 MHz) ou CLOCK_27 (27 MHz), conforme decisão de projeto;

- O reset é um sinal de 1 bit e deve ser obtido a partir do KEY(0);

- A frequencia a ser medida é um sinal de entrada de 1 bit, e pode ser o sinal EXT_CLOCK (clock externo). O sinal EXT_CLOCK está conectado ao pino PIN_P26 do FPGA da placa DE2. Para maiores informações sobre esse sinal, ver a página 33 do DE2 User Manual;

- As saídas são os cinco displays de 7-segmentos HEX0, HEX1, HEX2, HEX3 e HEX4, sendo que cada uma das saídas possui 7 bits. O expoente deve ser apresentado em HEX4, e a mantissa nos demais displays. O dígito mais significativo da mantissa deve ser representado em HEX3, e o menos significativo em HEX0.

Teste e validação

Utilizar o simulador com formas de onda para verificar o funcionamento do circuito, antes de testar na placa com FPGA.

Foi criado um script para automatizar o processo de criação da janela de formas de onda do Modelsim. Para utilizar o script, basta alterar o arquivo fornecido de acordo com os sinais a serem simulados no projeto em questão.

Algumas dicas:

- Utilizar o arquivo (script) compila.do como base.

- Esse script foi preparado para realizar a simulação do fonte VHDL teste.vhd, também disponível para download.

- O arquivo teste.vhd foi preparado para servir como exemplo de um fonte ?VHDL a ser simulado com o script compila.do, e a entity do teste.vhd possui os mesmos sinais esperados no topo do projeto final da disciplina.

- Para utilizar o script fornecido:

- Copiar o arquivo compila.do para a mesma pasta onde se encontra o projeto VHDL (arquivos a serem simulados)

- Editar o arquivo compila.do, e realizar as alterações necessárias, de acordo com seu projeto (alterar nomes de sinais, duração da simulação, valores dos sinais de entrada, sinais de clock, reset, …).

- No Quartus II, após realizar a síntese (compile), selecionar a opção para simulação conforme descrito no livro – RTL simulation

- Quando o Modelsim for executado, mudar para o diretório de trabalho onde se encontram os arquivos de projeto: Menu File -> Change directory – selecionar a pasta onde se encontra o projeto VHDL (arquivos a serem simulados e arquivo compila.do)

- Na linha de comando do Modelsim digitar o comando: do compila.do

- Ao ser executado, o script irá inicializar a simulação, criar a janela de formas de onda, colocar os sinais indicados na janela de forma de ondas, definir valores para os sinais, executar um passo de simulação, definir novos valores (force) para os sinais, realizar mais um passo de simulação, …

Documentação do projeto (relatório final)

- A documentação deverá ser completa e clara o suficiente para possibilitar alterações e atualizações na implementação do projeto, sem a necessidade de consultar os projetistas. Durante a correção da documentação o professor da disciplina irá realizar uma alteração no código VHDL, sem consultar os autores, com informações obtidas apenas a partir da documentação. Na avaliação final da documentação será considerado o grau de facilidade para realizar a alteração no VHDL.

- A documentação do projeto deverá conter uma descrição detalhada de todos os módulos desenvolvidos.

- O texto deverá DESCREVER o projeto, sem incluir a listagem completa do código VHDL implementado. Alguns trechos do código VHDL poderão ser incluídos na documentação, apenas quando necessário para alguma explicação de módulos implementados.

- Deverá ser incluído o fluxo completo do projeto, detalhando as ferramentas utilizadas e as etapas de projeto. A descrição do fluxo deve ser suficientemente detalhada de forma a facilitar a repetição de todas as etapas realizadas. No momento da correção do trabalho será consultada e seguida a descrição do fluxo de projeto existente na documentação. Dessa forma, descrições incompletas do fluxo de projeto poderão prejudicar a avaliação do trabalho.

- Preparar e incluir na documentação um diagrama de blocos completo com todos os módulos implementados. O diagrama de blocos deverá ser detalhado de forma a incluir todos os sinais de entrada e saída, e todos os módulos implementados.

- Deverá ser fornecida também a representação gráfica das máquinas de estados, tabelas de estados e explicações sobre estados e transições.

- Sugestão de organização para o documento do projeto:

- Folha de rosto contendo dados do autor, da instituição, local, data;

- Objetivos do trabalho;

- Especificação do problema proposto – visão/entendimento do autor sobre essa especificação;

- Projeto dos componentes do sistema com uma breve descrição do objetivo de cada componente. Incluir nessa descrição uma explicação (com diagrama de blocos e textual) dos componentes estudados na teoria e sua utilização na prática (ex. registradores, decodificadores, circuitos aritméticos, …);

- Descrição das ferramentas utilizadas e fluxo de projeto;

- Descrição da simulação realizada, com diagramas de forma de ondas extraídos diretamente do ModelSim;

- Considerações e conclusões sobre o trabalho realizado.

- É importante cuidar a coerência e a coesão da documentação, pois o documento entregue será essencial para o entendimento e correção do trabalho realizado.

- A documentação deverá ser entregue no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.OBSERVAÇÃO IMPORTANTE!! O trabalho pode ser realizado em grupo, porém A AVALIAÇÃO É INDIVIDUAL. Cada integrante do grupo SERÁ QUESTIONADO INDIVIDUALMENTE, e deverá estar apto A UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULAÇÃO REALIZADA.

Código fonte VHDL e arquivo de projeto do Quartus II

- O código fonte VHDL deve estar adequadamente comentado – incluir um comentário explicativo em cada bloco de código e, sempre que necessário, em linhas individuais.

- Incluir um bloco de comentário no início do arquivo com o fonte VHDL contendo dados dos alunos e demais dados de identificação do projeto (ex. utilidade, ferramentas, FPGA alvo, …).

- O código fonte precisa estar com a indentação adequada.

- Escolher nomes adequados para os símbolos utilizados no programa (entities, architectures, signals, …).

- Os fontes VHDL deverão ser entregues no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.

- Gerar um arquivo compactado, contendo APENAS os fontes VHDL do projeto desenvolvido no Quartus II, e submeter apenas esse arquivo. O sistema de submissão de trabalhos disponível no Moodle aceitará a submissão de um único arquivo por grupo. Foi definido um tamanho máximo de arquivo que pode ser submetido, para garantir que o aluno irá enviar APENAS os fontes VHDL compactados em um único arquivo.

Etapas do projeto e dicas úteis

1. Dividir o problema em partes menores – abordagem “dividir para conquistar”:

- Desenvolver em VHDL e simular (diagrama de formas de onda) os componentes solicitados no trabalho. Durante o semestre, alguns desses circuitos foram desenvolvidos nas aulas teóricas e práticas como, por exemplo, registradores e máquinas de estados.

- Desenvolver e simular (diagrama de formas de onda) os circuitos combinacionais em VHDL para as operações lógicas e aritméticas a serem executadas.

- Seguir as dicas para implementação de circuitos controladores fornecidas nas aulas teóricas e práticas. Uma boa dica de descrição em VHDL de uma FSM de controlador é desenvolvida no Laboratório 8.

- Após ter certeza que todos os circuitos possuem o comportamento desejado, realizar a integração dos componentes desenvolvidos, formando gradualmente sistemas digitais mais completos que atendam aos requisitos fornecidos. A integração de componentes é realizada com port map, e foi apresentada e praticada desde o início do semestre a partir do Laboratório 3.

- Seguindo essa filosofia de projeto, poderia ser desenvolvida uma versão inicial do circuito com apenas uma funcionalidade e, após devidamente validada, as demais funcionalidades poderiam ser incluídas. Os componentes podem ser validados individualmente, antes de serem anexados ao projeto. Uma sugestão é comentar os port maps onde as conexões dos componentes são definidas, e ir removendo os comentários de forma a incluir os componentes gradualmente no circuito. As entradas dos componentes podem ser exercitadas por intermédio de chaves e botões, e as saídas podem ser observadas nos LEDs e LCD. Quando um componente é anexado ao circuito, essas entradas e saídas devem ser substituídas pelos sinais adequados da FSM de controle.

- ATENÇÃO!! Mesmo projetistas de sistemas digitais experientes, já atuando na indústria, não desenvolvem sistemas por inteiro sem antes simular e validar os componentes individualmente. Essa regra é seguida por projetistas experientes até para sistemas digitais considerados simples como, por exemplo, o projeto em questão.

2. Simulação do projeto:

- Utilizar ferramentas de simulação com formas de ondas, tais como, o ModelSim para simular os circuitos desenvolvidos individualmente.

- Realizar a simulação com os diagramas de formas de ondas dos diversos componentes desenvolvidos e, gradualmente, dos novos componentes compostos pela integração dos componentes menores, até chegar na implementação final do projeto.

- A simulação individual dos componentes é importante durante as etapas de desenvolvimento, mas apenas a simulação final com todos os componentes integrados (simulação do topo) pode ser considerada na validação final do projeto.

3. Prototipação na plataforma de desenvolvimento:

- Identificar os periféricos disponíveis no kit de desenvolvimento e pinos de entrada/saída, que poderão ser úteis no desenvolvimento do sistema digital solicitado.

- Testar na plataforma de desenvolvimento os diversos componentes conforme forem sendo desenvolvidos, assim como os componentes resultantes da integração dos módulos. Realizar os testes na plataforma de desenvolvimento, apenas após a simulação (diagramas de formas de onda) indicar que o sistema está funcionando de acordo com o esperado.

- As plataformas de desenvolvimento do laboratório não poderão ser emprestadas para os alunos, que deverão compartilhar as mesmas apenas no laboratório.

4. Ajuda:

- Procurar o monitor da disciplina para dúvidas sobre o projeto dos circuitos a serem utilizados.

- Verificar a agenda semanal do Prof. Eduardo Bezerra para combinar horários de atendimento e, também, para agendar a data/hora da apresentação do trabalho:

(selecionar week view)

(selecionar week view)

Avaliação

- O trabalho poderá ser desenvolvido individualmente ou em grupos com, no máximo, três integrantes.

- O relatório é individual. Cada aluno da turma deverá preparar seu próprio relatório, expressando a sua opinião.

- O código VHDL pode ser o mesmo para todos os alunos de um mesmo grupo.

- Será avaliado, principalmente, o funcionamento de todos os componentes funcionando em conjunto, ou seja, a principal simulação a ser apresentada é a do arquivo “topo”. É preciso mostrar que a FSM está controlando adequadamente todos os demais componentes do circuito, com o mesmo clock sendo aplicado a todo o projeto (isso só é possível de ser observado no topo).

- A documentação do projeto e o fonte VHDL deverão ser entregues no Moodle:

- A entrega dos fontes VHDL e do relatório será realizada no Moodle.

- Não serão aceitos envios atrasados. O sistema do Moodle irá bloquear automaticamente após o prazo final da entrega.

- Em semestres anteriores, alunos que perderam o prazo para envio ficaram com nota zero no trabalho final.

- O sistema aceita vários envios (desde que dentro do prazo de entrega). Assim, é fortemente recomendado que todas as versões parciais do trabalho sejam enviadas no moodle (tanto o VHDL quanto o relatório).

- Uma nova submissão sobreescreve a anterior. Todos os alunos devem submeter pelo menos uma versão dos seus trabalhos por dia, garantindo que terá um trabalho para ser avaliado no final do semestre.

- O tamanho máximo do arquivo contendo o relatório é de 1 M bytes. Deverá ser submetido APENAS um arquivo, e esse arquivo deverá estar no formato PDF.

- O tamanho máximo do arquivo contendo os fontes VHDL é de 100 K bytes. Deverá ser submetido APENAS um arquivo compactado contendo todos os fontes VHDL.

- Não deverão ser incluídos arquivos de projeto do Quartus II no arquivo compactado – INCLUIR APENAS OS FONTES VHDL (.vhd).

- O nome do arquivo compactado com os fontes VHDL deverá ser o nome completo do aluno, sem espaçamento. Por exemplo, o aluno “Eduardo Augusto Bezerra” deverá gerar o seguinte arquivo compactado com seus fontes VHDL: “EduardoAugustoBezerra.zip”

- TODOS OS ALUNOS DEVERÃO SUBMETER OS SEUS RELATÓRIOS E FONTES VHDL, MESMO QUE TENHAM DESENVOLVIDO OS TRABALHOS EM GRUPOS.

- O sistema de submissões de arquivos do Moodle é a ferramenta oficial para entrega de trabalhos da disciplina. NÃO SERÃO ACEITOS TRABALHOS ENVIADOS POR EMAIL, TRABALHOS IMPRESSOS, OU QUALQUER OUTRA FORMA DE ENTREGA A NÃO SER O SISTEMA DO MOODLE.

- A apresentação da simulação e a demonstração do funcionamento por intermédio de simulação será realizada nas semanas indicadas no cronograma das aulas. Os alunos deverão agendar a data e hora para apresentação do trabalho diretamente na agenda do Google, conforme instruções enviadas por email para todos os alunos.

- Durante a apresentação, os alunos deverão estar aptos a responder quaisquer perguntas. Respostas insatisfatórias ou a ausência do aluno poderá acarretar em anulação da nota final.

- Na apresentação serão realizados questionamentos sobre decisões de projeto e estratégias de implementação VHDL utilizadas. Será verificada também a familiaridade dos alunos com as ferramentas de desenvolvimento utilizadas durante o semestre. Todos os alunos devem estar aptos a responder todas as questões.

- As explicações durante a apresentação da documentação do projeto, e na demonstração do projeto funcionando por intermédio da simulação e dos diagramas de formas de onda, são fundamentais para a avaliação.

- Trabalhos copiados, inclusive entre turmas, resultarão em nota zero para todos os alunos envolvidos. Será utilizado o MOSS como ferramenta auxiliar na identificação de situações de plágio. Obviamente, similaridade de 100% nos fontes VHDL de um mesmo grupo é um resultado esperado. O mesmo não se espera em relação aos relatórios, que deverão ser diferentes mesmo entre integrantes do mesmo grupo.

- Os dois itens a serem avaliados possuem os seguintes pesos na nota final do trabalho prático:

- Documentação do projeto: 40%

- Demonstração do funcionamento por intermédio de simulação: 60%

- OBSERVAÇÃO IMPORTANTE!! O trabalho poderá ser realizado em grupo, porém A AVALIAÇÃO É INDIVIDUAL. Cada integrante do grupo SERÁ QUESTIONADO INDIVIDUALMENTE, e deverá estar apto A UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULAÇÃO REALIZADA. Cada integrante do grupo deverá reservar um horário em separado para sua apresentação.