by

Filipe D. de Moraes, Luis F. A. Guedes e Tiago Jost

![]()

1. Introdução ao 8051

Primeiramente iremos

esclarecer a diferença entre um microcontrolador e um

microprocessador.

Microprocessador: chip responsável pelo

processamento em um microcomputador. É um elemento complexo, contendo, entre

outras coisas, uma unidade lógica e aritmética (ULA) e diversos registros

(registradores) especiais.

Microcontrolador: chip que pode conter,

além de um microprocessador, periféricos, tais como timers,

interfaces seriais, conversores, etc.

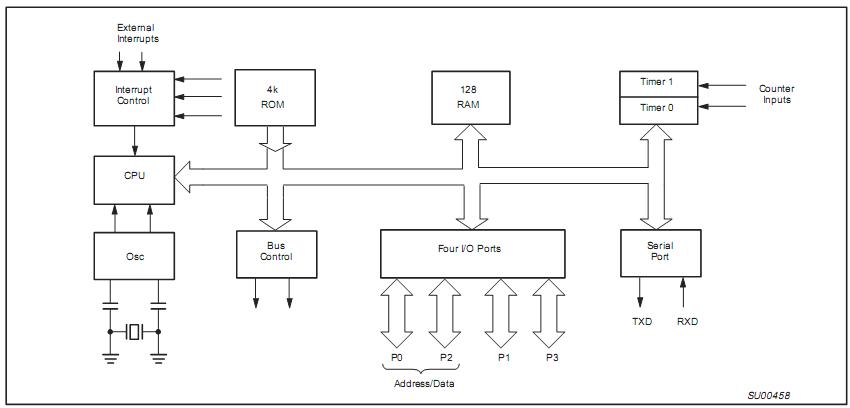

Figura 1 – Diagrama de blocos

O 8051é sem dúvida, o microcontrolador mais popular atualmente. O dispositivo em

si é um microcontrolador de 8

bits relativamente simples, mas com ampla aplicação. O mesmo tem dois modos

básicos de funcionamento:

a) modo mínimo, onde

somente recursos internos são utilizados pela CPU. Neste modo, estão

disponíveis 4 KB de ROM para memória de programa e 128 bytes de RAM para

memória de dados.

b) modo expandido. Neste

modo, a memória de programa (ROM), a memória de dados (RAM) ou ambas podem ser

expandidas para 64 kB,

através do uso de CIs externos. No entanto, apresenta

a desvantagem de "perder" duas das 4 portas

para comunicação com as memórias externas.

Tempos da CPU:

a)Ciclo de Máquina: 12

ciclos de clock (sem pipeline).

Consiste

Set de Instruções:

a)O 8051 possui um extenso

conjunto de instruções, apresentando diferentes tamanhos(bytes) e CPI(ciclo por

instrução).

Modos de Endereçamento:

a)Modo Direto, modo

Registrador, modo Indireto, modo Específico a Registro, imediato e Indexado.

Detalhamentos serão

abordados no momento oportuno. Periféricos não serão estudados.

2. Modelo super simplificado do microcontrolador 8051: PPG2 – Pipelined

Processor Grupo 2

O objetivo deste

trabalho é implementar em VHDL uma versão super simplificada da arquitetura do microcontrolador

8051, adicionando a ela o recurso de pipeline,

devendo contemplar a detecção e tratamento de hazards,

stalls, possuindo uma unidade de forwarding.

Desse modo, o que se

pretende obter é a descrição de hardware comportamental para um

microprocessador com pipeline, e não a de um microcontrolador, mantendo a capacidade de executar

programas em assembly para o 8051, respeitando o

suporte as instruções e aos modos de endereçamento.

3. Especificação da Arquitetura – Overview

Propomos um processador de 8

bits, baseado na arquitetura Harvard com pipelining

de 3 estágios. Semelhante ao 8051, sua estrutura será

baseada em acumulador (registrador ACC) e terá 7 registradores auxiliares (R0 a

R6), usando apenas um banco, mais o registrador de função especial PSW(STATUS).

A palavra de programa é de 16 bits e a memória de programa endereçada por 8 bits.

No tópico

4.

Conjunto de Instruções

O conjunto de instruções(instruction set) do processador será composto por 8

instruções: 1 aritmética, 2 lógicas, 1 salto incondicional, 2 saltos

condicionais, 1 bolha (nop) e 1 move. Seus mnemônicos

são:

ADD, ANL, CPL, JMP, JZ, JC, NOP e MOV

A palavra de programa possui tamanho fixo para

qualquer instrução: 16 bits. A codificação das instruções se dá pela divisão da

palavra de programa em 5 campos, tal como é mostrado

abaixo:

|

OP |

AM |

RTM |

SRC |

DST |

|

3bits |

1bit |

1bit |

3bits |

8bits |

Entendendo

o significado de cada campo:

OP(Opcode)

|

MNEMONICO |

OPCODE |

|

NOP |

000 |

|

MOV |

001 |

|

JMP |

010 |

|

JC |

011 |

|

JZ |

100 |

|

ADD |

101 |

|

ANL |

110 |

|

CPL |

111 |

AM (Address Mode)

0-DIRETO

1-IMEDIATO

RTM (Register to Memory)

0- o source

é registrador (REG -> MEM) (3 primeiros bits)

1- o source é end. memória (MEM -> REG) (8

primeiros bits)

SRC (Source)

3 bits se RTM=0

8 bits se RTM=1

DST (Destiny)

8 bits se RTM=0

3 bits se RTM=1

Ir para Conjunto de Instruções.

5. Modos

de Endereçamento

Os modos de endereçamento suportados por esta

arquitetura são dois: imediato e direto.

Endereçamento Imediato

Opera sobre o dado localizado na própria

instrução.

Identificado através do sinal # (cerquilha).

Exemplo: ADD A, #30

O valor 30 é somado ao acumulador.

Endereçamento Direto

Opera sobre o dado cujo endereço está na

instrução.

Exemplo: ADD A, 30

O dado armazenado no endereço 30 é somado ao

acumulador.

6. Banco

de registradores

O banco de registradores é a parte de locação de

memória RAM, que denominamos REGISTRO ou Memória de Dados. Esta área de memória

RAM, a partir do endereço 01H é igualmente visível pelo resto do programa.

Nessa área pode-se escrever, ler e modificar qualquer endereço a qualquer

momento.

A limitação existente consiste no fato de que um

registrador desenvolve função especial (SFR) pelo processador e não pode ser

utilizado para fins diferentes para aquilo que está reservado. Este registrador

encontra-se na locação base (endereço iniciai) da área de memória RAM, segundo

ilustrado abaixo:

|

Bank 0 |

|

|

SFRs |

Address |

|

Indirect Address* |

00H |

|

PSW(status) |

01H |

|

R0 |

02H |

|

R1 |

03H |

|

R2 |

04H |

|

R3 |

05H |

|

R4 |

06H |

|

R5 |

07H |

|

R6 |

08H |

|

General Purpose |

09H |

|

... |

... |

|

General Purpose |

FFH |

As locações de memória RAM presente no REGISTRO

são endereçadas contiguamente em um espaço de memória que vai de 00H* a FFH,

totalizando 256 bytes, que chamamos de Banco 0. Este

conceito de banco (ou página) é um legado das arquiteturas do 8051, que em sua

versão clássica possui 4 bancos de registradores, e da arquitetura dos uControladores PIC.

As 2 primeiras locações

são reservadas para os Registradores de Função Especiais (SFRs),

dos quais falaremos a seguir. As 7 locações seguintes

se destinam aos registradores auxiliares.

As demais 247 locações podem ser usadas

livremente pelo programa como memória de dados.

7. Especificação

da Arquitetura PPG2 – parte 2

Para acessar a especificação completa da

arquitetura PPG2, clique

aqui!

8. Programando

para o PPG2

Para acessar este conteúdo, clique aqui!

![[Envie suas críticas, sugestões ou dúvidas]](index_files/email.jpg)