by

Filipe D. de Moraes, Luis F. A. Guedes e Tiago Jost

![]()

7. Especificação da

Arquitetura PPG2 – parte 2

Até o momento falamos de

algumas características e recursos do PPG2, porém, sem fornecer detalhes de seu

modelo e de sua construção.

Neste tópico será

explicado cada bloco do processador já com pipelining

implementado.

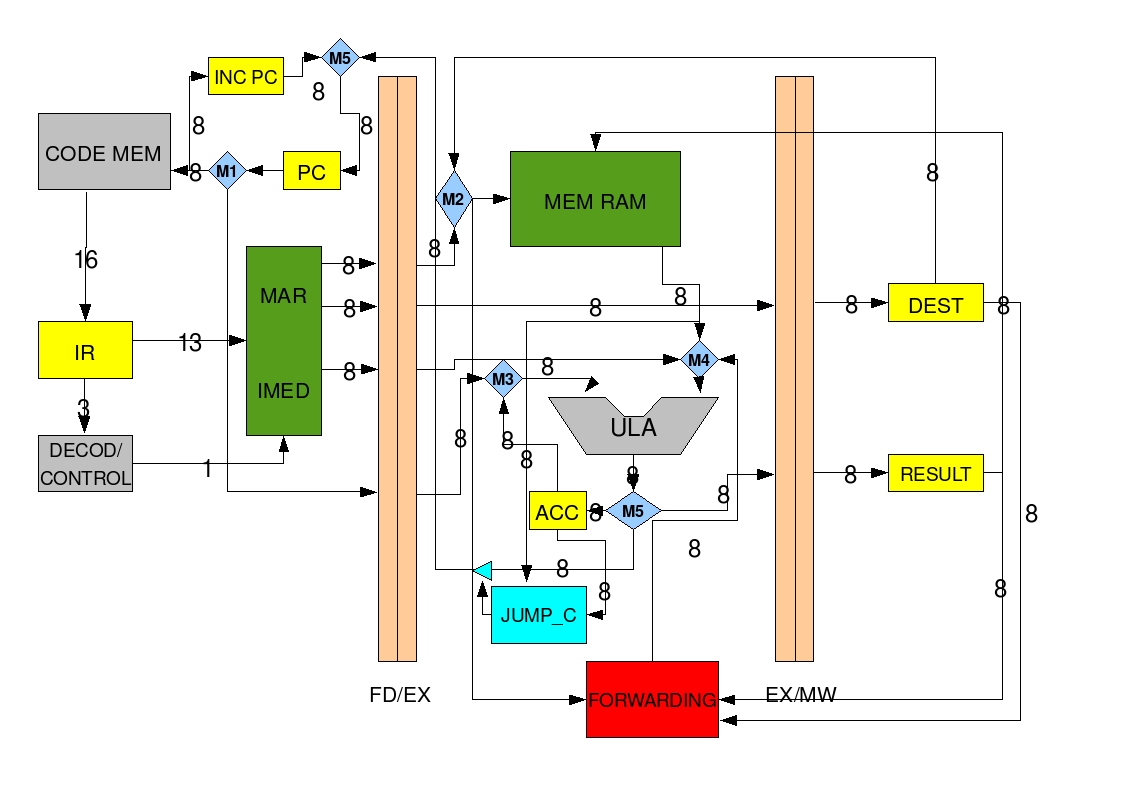

Figura 2 – Arquitetura PPG2

Code Memory (Memória de Programa)

Este bloco corresponde a memória de programa, que é o local onde se armazena as

instruções a serem executadas pelo processador. Esta memória é endereçada pelo PC(Program Counter)

e lida pelo registrador de instruções. É endereçada por 8

bits e a palavra de programa é de 16bits, que formará uma ROM emulada de

256x16bits.

Instruction Register - IR(Registrador

de instrução)

Bloco conhecido como Instruction Register(Registrador de Instrução). Aqui a instrução buscada na memória

de programa é pré-decodificada, pois o código binário da instrução é dividido

em campos e redirecionada para o bloco de decod/control(decodificação

e controle): 3 MSB e para o MAR(memory access register):13 MSB.

Decod/Control

Realiza a decodificação

do opcode das instruções, sincroniza e controla o

fluxo dos dados, gerenciando, junto ao MAR, todas as tarefas do processador(core).

MAR/IMMED

Um dos blocos mais

importantes do ciclo de FD(FETCH/DECOD). Dois bits são

responsáveis por controlar este bloco: MA(memory address,bit 12) e RTM(register to memory,bit 11), que

configuram o modo de endereçamento e o sentido do "writeback"

de algumas instruções (Rn->Mem ou Rn<-Mem), respectivamente. Além disso, este bloco contém um

modulo de Zero Extend para o endereçamento dos

Registradores auxiliares, que são endereçados por 3

bits da instrução (campos SRC ou DST, conforme RTM), enquanto a memória é

endereçada diretamente por 8 bits.

Program Counter – PC (Contador de

Programa) e INC

PC

O processador possui um

registrador chamado PC (Program Counter)

que contém o endereço da próxima instrução que deve ser executada. Toda vez que

uma instrução é retirada da memória, automaticamente o contador de programa é incrementado (bloco

inc pc), para que, no próximo ciclo, quando for

buscada a próxima instrução, baste usar o endereço contido no registrador PC.

Em casos de salto, é somado ao registrador o offset

de deslocamento contido na própria instrução. A seleção entre o inc pc(PC+1)

e o incremento de offset(PC+offset)

é feito pelo mux M6, que é controlado pelo bloco de

tratamento de saltos JUMP_C. Como o cálculo e análise do cálculo será feito no proximo ciclo de clock, foi

decidido por convenção no projeto, nunca saltar antes de verificar o salto,

caso o salto tenha sido errado é feito o flush da instrução errada e então é

realizado o salto.

Registrador ACC

É um registrador/memória

de 8bits localizado fora da área da memória de dados. Sua principal função é

auxiliar nas operações da ALU

Arithmetic and Logical

Unit – ALU (Unidade Lógica e Aritmética)

Unidade que executa as

operações lógico-aritméticas durante a execução de uma instrução. O resultado

de uma operação da ALU pode ter como destino o registrador ACC ou uma

localidade da memória

de dados. Possui um registrador de status para as suas operações(SFR

- special function register): PSW, localizado no endereço 01H da memória de dados.

Data Memory – RAM (Memória

de dados)

É a parte de locação de

memória RAM, que denominamos REGISTRO ou Memória de Dados. O endereço 00H é

reservado e não está acessível. A partir

do endereço 01H é igualmente visível pelo resto do programa. No endereço 01H está localizado o registro de

status PSW. Nos endereços subseqüentes, até 08H, estão os Registradores

Auxiliares R0 a R7. Do endereço 08H até

FFH está localizado o espaço de memória de uso geral. Nessa área pode-se escrever, ler e modificar qualquer endereço a qualquer

momento. As locações de memória RAM presente no REGISTRO são endereçadas

contiguamente em

um espaço de memória que vai de 00H* a FFH, totalizando 256 bytes, que chamamos

de Banco 0.

Multiplexadores

e Demultiplexadores – M1 a M6

Os multiplexadores e demultiplexadores são utilizados para que não haja dois barramentos acionados ao mesmo tempo, o que poderia ocasionar um curto circuito nos barramentos. No PPG2 foram utilizados 6 multiplexadores para manter o fluxo de informações, são eles:M1: Faz a seleção de o PC será escrito no pipe ou endereçará a memória e escreverá no INC_PC.

M2: Faz a seleção de se a MEM RAM será lida ou escrita.

M3: Faz a seleção de qual dado será colocado na entrada A da ULA, se é o ACC ou o PC.

M4: Faz a seleção de qual dado será colocado na entrada B da ULA, se é um dado imediato, um dado da memória ou um dado adiantado pela unidade de FORWARDING.

M5: Faz a seleção do registrador em que será escrito o resuiltado da ULA, se no ACC, no pipe ou no PC.

M6: Faz a seleção de dado será escrito no PC, pode ser o INC PC ou o resultado da ULA.

Pipelining

O pipeline do PPG2 é constituído por 3

estágios: FD (Fetch, Decod),

EX (Execution), MW (Memory Write). Sendo esta uma estrutura pipeline

de 3 estágios, *a partir* do terceiro ciclo de clock da execução do processador teremos simultaneamente 3

instruções ao mesmo tempo no core do processador. Isto é possível pois a cada ciclo de clock a

instrução avança de um estágio para o outro, usando para manter seus dados

estáveis e organizados a "barreira de pipe",

que são registradores utilizados apenas para este propósito e que estão

situados na divisa de cada mudança de estágio do pipeline.

No estágio FD as instruções são buscadas da memória de programa e

decodificadas, sendo todos os dados direcionados para seus respectivos

destinos. No estágio EX as informações enviadas pelo estágio FD são

processados, tendo também acesso a memória de dados para obtenção de operandos. No estágio MW é feito o

endereçamento e escrita da memória de dados, se for necessário para a

instrução.

Forwarding

Nas

arquiteturas baseadas em pipeline é muito comum haver

problemas de leitura de um dado ainda não processado, ou não escrito na posição

de memória que está sendo lida por uma outra instrução. Existem varias formas

de resolver tais problemas, pode se utilizar "bolhas", que são

instruções que não fazem alteração nenhuma nos registradores ou na memória.

Outra forma de resolver tais problemas é se utilizar uma unidade de

"adiantamento", seria esta uma unidade que pega a informação pronta

que saiu da ULA ou que está pronta para ser escrita na memória e a direciona

direto para o estágio em que ela é nescessária. No

caso do PPG2 utilizamos uma unidade de adiantamento, que verifica se o dado que

está pronto para ser escrito na memória não é o dado nescessário

para a proxima instrução, se for esse o caso então o

dado é "mandado" para a entrada da ULA no mesmo instante em que é

escrito na memória, não prejudicando assim a progressão do pipeline.

Jump_c –

Controle de saltos

A unidade

de controle de saltos é uma unidade que verifica se um salto condicional será

realizado ou não. Ele recebe os valores de controle do registrador PSW e também

o conteúdo do ACC após fazer os testes ele permite ou não a

passagem do endereço calculado pela ULA, ele faz tal controle através de um

sinal de controle para um tri-state que pode permitir

a passagem para escrever no PC ou colocar o barramento

em alta impedância. Caso o salto não seja condicional, a unidade de controle de

saltos permite a escrita no PC sem fazer teste algum.

Pop-up para comentários. Clique aqui!