|

EEL 4100 38 - Sistemas Digitais e Dispositivos Lógicos Reconfiguráveis

Prof. Eduardo Augusto Bezerra - Eduardo.Bezerra @ eel.ufsc.br

Prof. Djones Vinicius Lettnin - Lettnin @ eel.ufsc.br

Programa de Pós-Graduação em Engenharia Elétrica

Departamento de Engenharia Elétrica,

CTC,

UFSC,

Florianópolis, SC, Brasil

Especificação do Trabalho Final - Período 2012/2

"Projeto e implementação em VHDL para FPGAs de arquitetura com conjunto super-reduzido de instruções"

|

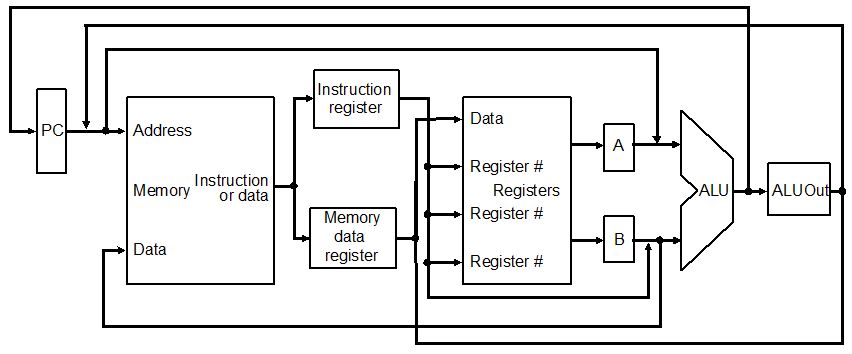

A CPU de uma determinada arquitetura possui os seguintes componentes:

Registrador PC (program counter) - contém o endereço da próxima instrução a ser executada;

Registrador IR (instruction register) - contém a instrução de máquina em execução na arquitetura em um determinado instante;

Registrador A - armazena resultados intermediários de operações (acumulador);

Registrador B - armazena resultados intermediários de operações (auxiliar);

Memória de dados;

Memória de instruções;

Conjunto de instruções de 16 bits listadas na tabela a seguir, onde end representa um endereço de memória de 8 bits ou don't care para as instruções que não realizam acesso a memória.

|

Tipo

|

Código de máquina

|

Instrução

|

Operação

|

Descrição

|

|

I

|

00000001 end

|

LDA end

|

A <= memória[end]

|

Registrador A recebe o conteúdo da posição de memória end

|

|

I

|

00000010 end

|

STA end

|

memória[end] <= A

|

Posição de memória end recebe o conteúdo do registrador A

|

|

I

|

00000011 end

|

BLT end

|

PC <= (A < B ? end : PC + 2)

|

A execução do programa é desviada para o endereço end, se A for menor do que B

|

|

I

|

00000100 end

|

BEQ end

|

PC <= (A == B ? end : PC + 2)

|

A execução do programa é desviada para o endereço end, se A for igual a B

|

|

J

|

00000101 end

|

JMP end

|

PC <= end

|

A execução do programa é desviada incondicionalmente para o endereço end

|

|

R

|

00010000 end

|

ADD

|

A <= A + B

|

Registrador A recebe a soma de A com B (complemento de 2)

|

|

R

|

00100000 end

|

MUL

|

AB <= A * B

|

Multiplicação de A com B, sendo que o registrador A recebe a parte baixa do resultado, e o registrador B a parte alta

|

|

R

|

00110000 end

|

AND

|

A <= A AND B

|

Registrador A recebe o resultado da operação lógica AND de A com B

|

|

R

|

01000000 end

|

OR

|

A <= A OR B

|

Registrador A recebe o resultado da operação lógica OR de A com B

|

|

R

|

01010000 end

|

NOT

|

A <= NOT A

|

Registrador A recebe o conteúdo de A negado

|

|

R

|

01100000 const

|

LI const

|

A <= constante

|

LSB do registrador A recebe o valor constante contido na instrução, e MSB do A recebe 0 (zero)

|

|

R

|

01110000 end

|

SWP

|

A <= B, B <= A

|

O conteúdo do registrador A é copiado para o registrador B, e vice-versa (swap A, B)

|

|

|

11111111 end

|

HALT

|

Halt

|

Suspende a execução do processador

|

Na coluna "Tipo" são listados os seguintes tipos de instruções:

- I - instruções do tipo I utilizam um endereço de memória para transferência de dados (STA e LDA) ou para desvio condicional do fluxo de execução do programa (BRN e BRZ)

- J - instruções do tipo J realizam um desvio incondicional para o endereço especificado na própria instrução

- R - instruções do tipo R realizam operações com operandos armazenados em registradores (não realizam acesso a memória)

Projetar e modelar a arquitetura em SystemC e, a seguir, implementá-la em VHDL visando síntese em FPGAs. Demonstrar o funcionamento da arquitetura por intermédio da execução de um programa nas plataformas de desenvolvimento disponíveis no laboratório.

Observações:

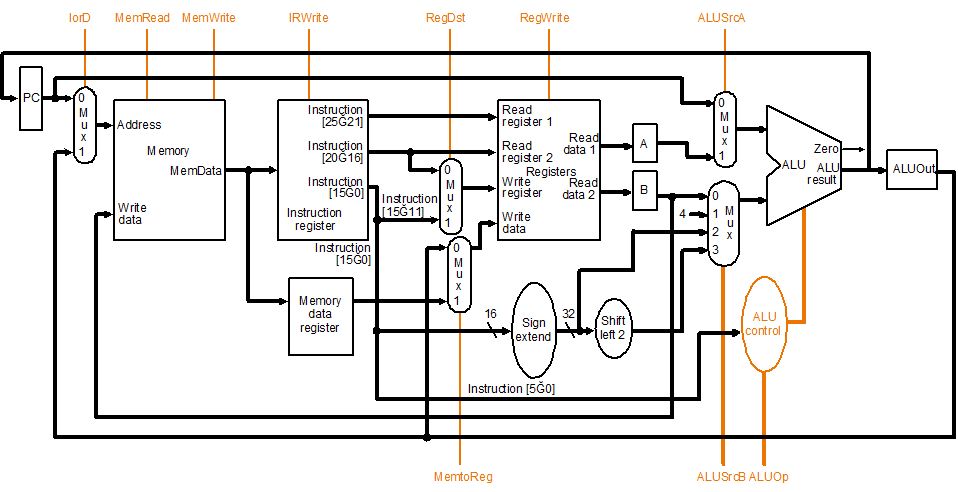

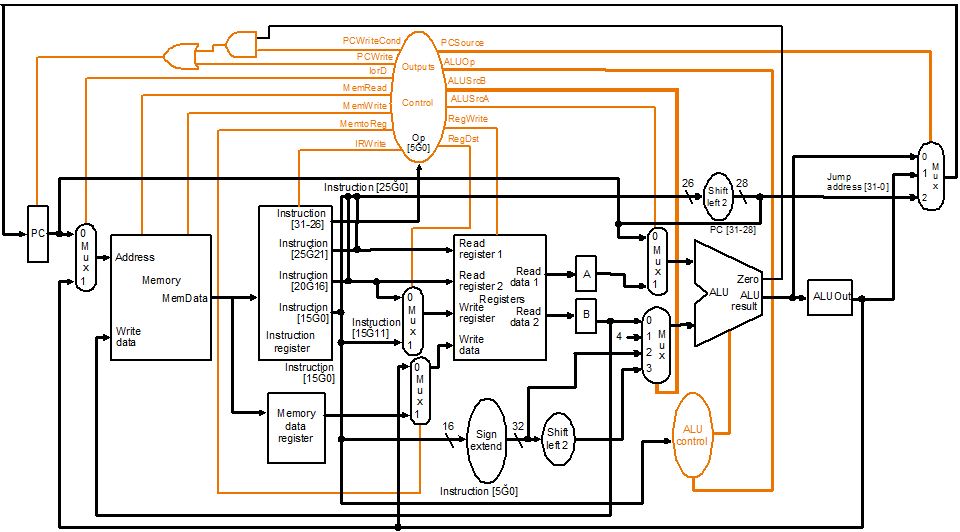

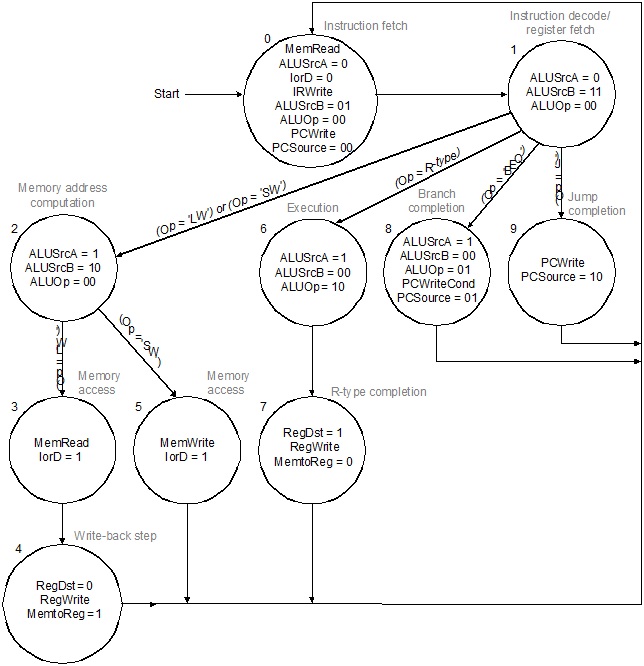

Utilizar como base a arquitetura MIPS multiciclo definida no livro do David A. Patterson e John L. Hennessy, “Computer Organization and Design: The Hardware/Software Interface”.

Definir uma faixa de endereços de memória para mapear, pelo menos, uma porta de entrada e uma porta de saída de 8 bits cada. Essas portas poderão representar, por exemplo, 8 chaves (entrada) e 8 LEDs (saída) do kit de desenvolvimento.

A ULA, além do resultado da operação realizada, deverá sinalizar também o resultado das operações de comparação realizadas.

Desenvolver um programa de teste, e executá-lo na arquitetura projetada. Esse programa de teste deve realizar algum processamento útil, sendo necessário consultar previamente os professores da disciplina sobre a validade do algoritmo selecionado.

O trabalho é individual.

A entrega/apresentação do trabalho será na aula do dia 13/09 (ou em data anterior a ser combinada entre aluno e professor).

Preparar uma documentação completa descrevendo a arquitetura do sistema, ferramentas utilizadas, e todos os componentes do VHDL. Descrever também o procedimento necessário para o desenvolvimento de programas para o microprocessador, incluindo detalhes sobre a definição dos conteúdos das memórias de dados e endereços. A documentação é parte fundamental da avaliação, e deverá ser preparada de forma a possibilitar futuras alterações no projeto.

A seguir estão incluídos alguns diagramas da arquitetura MIPS a ser utilizada como base para esse trabalho.

|