EEL-7020 - Sistemas Digitais

Definiçăo do Trabalho Prático - 2011/2

“Projeto, implementaçăo e simulaçăo em VHDL/FPGA de um circuito para o cálculo do consumo instantâneo de combustível em um veículo”

Departamento de Engenharia Elétrica,

CTC,

UFSC,

Florianópolis, SC, Brasil

Prof. Eduardo Augusto Bezerra

Prof. Joni da Silva Fraga

Prof. Djones Vinicius Lettnin

Eng. Frederico Ferlini

Visăo geral

O objetivo geral do trabalho prático é o projeto e implementaçăo em VHDL/FPGA de um circuito para calcular o consumo instantâneo de combustível em um veículo, por intermédio da multiplicaçăo de números năo inteiros utilizando a representaçăo em ponto flutuante.

Referencial teórico

1. Multiplicaçăo em binário - algoritmo soma e desloca:

- Um circuito para multiplicaçăo em binário aceita como entrada dois operandos de n bits cada um, fornecendo como saída um resultado de 2 * n bits. Por exemplo, considerando dois operandos de 8 bits cada um, o resultado da multiplicaçăo terá 16 bits.

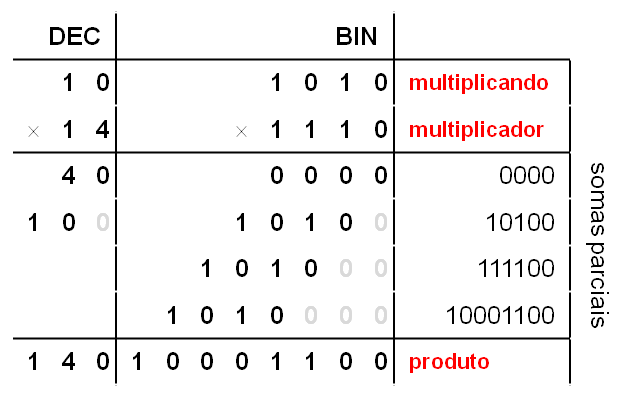

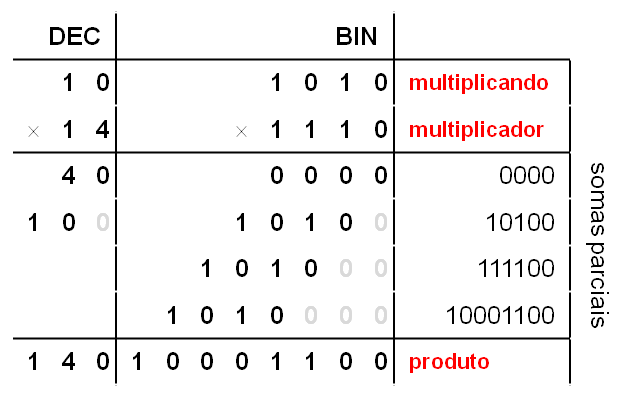

- A Figura 1 apresenta os passos da multiplicaçăo em binário realizada manualmente. Nesse exemplo, os operandos (multiplicando e multiplicador) săo os valores 10 e 14 em decimal (primeira coluna). Assim, a operaçăo a ser realizada consiste em 10*14 = 140. A coluna DEC apresenta os passos para a multiplicaçăo em decimal. A coluna BIN apresenta os passos para a multiplicaçăo em binário. A terceira e última coluna, apresenta os resultados parciais das multiplicaçőes em binário. A última linha apresenta o resultado final (produto) em decimal (primeira coluna) e binário (coluna do meio).

Figura 1. Exemplo de operaçăo de multiplicaçăo em decimal e em binário.

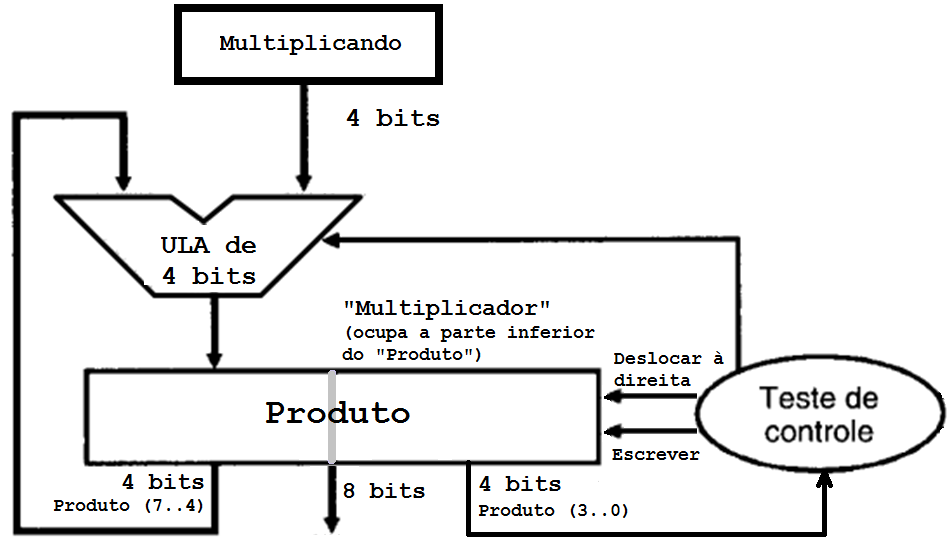

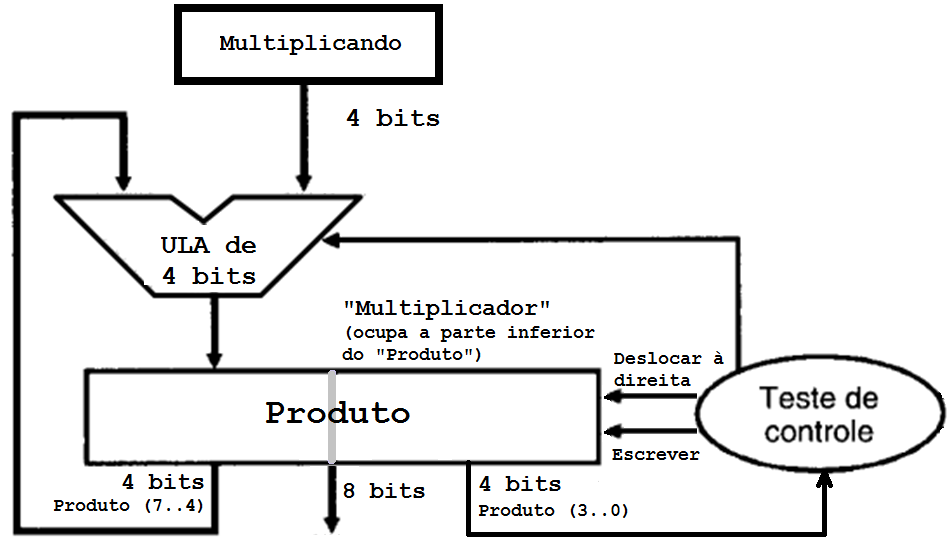

- Na Figura 2 é apresentado o diagrama de blocos de um circuito utilizado na execuçăo da multiplicaçăo de 4 bits descrita na Figura 1.

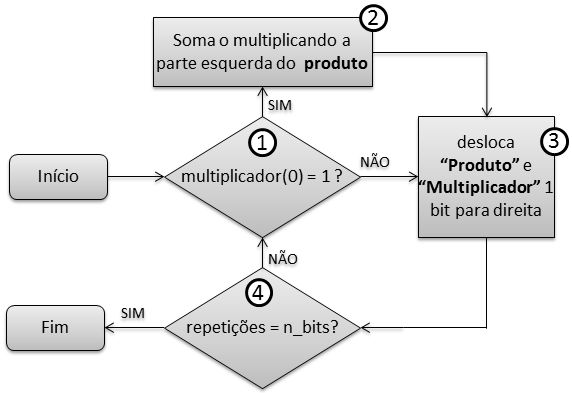

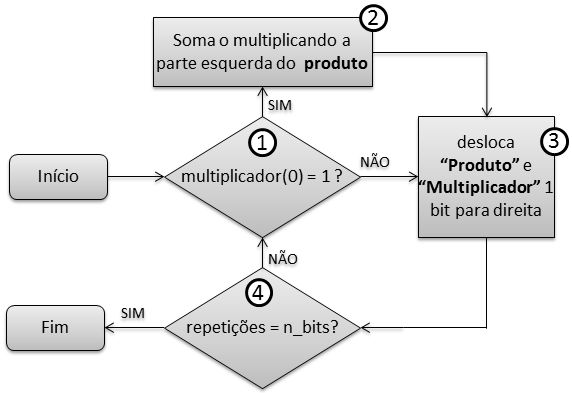

- A Figura 3 mostra o fluxograma do algoritmo de multiplicaçăo "soma e desloca" do circuito da Figura 2:

- Na Figura 2, o registrador "Multiplicando" de 4 bits é uma das entradas do somador (ULA), e a parte superior do registrador "Produto" (4 bits) é o segundo operando do somador.

- O "Multiplicador" está armazenado na parte inferior (4 bits) do registrador "Produto".

- Inicialmente, a parte superior do registrador "Produto" possui o valor zero ("0000").

- O algoritmo inicia verificando se o bit 0 (menos significativo) do "Multiplicador" (localizado no registrador "Produto"), possui o valor '1'.

- Se o bit 0 do "Multiplicador" for igual a '1', entăo o "Multiplicando" é adicionado ŕ parte superior do "Produto".

- Se o bit 0 do "Multiplicador" for igual a '0', entăo o "Multiplicando" NĂO é adicionado ŕ parte superior do "Produto".

- Em ambos os casos (Multiplicador(0) = '1' ou '0'), o registrador "Produto" (incluindo o registrador embutido "Multiplicador") é deslocado um bit ŕ direita.

- O teste (Multiplicador(0) = '1'), seguido da soma do multiplicando com o produto, e do deslocamento do "Produto", é repetido 4 vezes (n vezes), que é o tamanho do "Multiplicando" e do "Multiplicador".

- Após as n repetiçőes (4, no exemplo em questăo), o registrador "Produto" armazenará o resultado da multiplicaçăo.

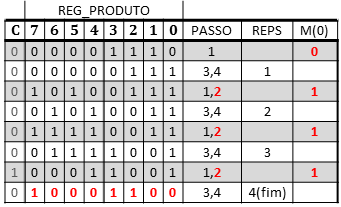

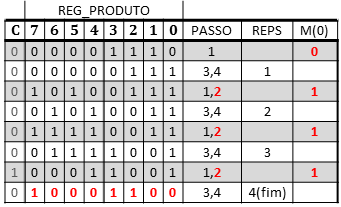

- A Figura 4 mostra o conteúdo do registrador "Produto" a cada passo do algoritmo.

Figura 2. Diagrama de blocos de circuito para multiplicaçăo de operandos de 4 bits.

Figura 3. Fluxograma do algoritmo de multiplicaçăo "soma e desloca" de um multiplicador de n bits.

Figura 4. Conteúdo do "registrador de produto" a cada etapa de execuçăo do algoritmo de multiplicaçăo "soma e desloca" de um multiplicador de 4 bits.

2. Representaçăo de números com vírgula em binário

- Ponto Fixo

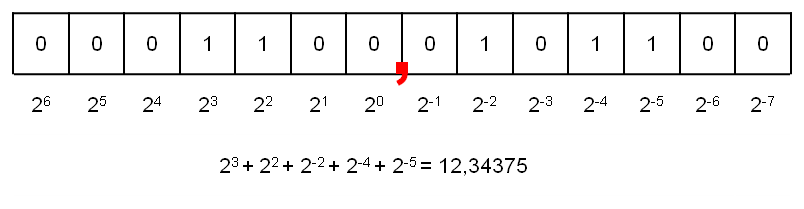

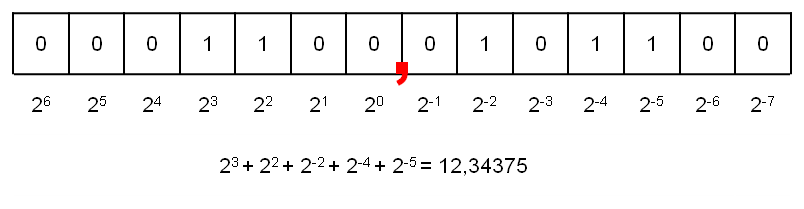

- Exemplo: representar 12,3456 em binário utilizando ponto fixo, sendo metade dos bits para parte inteira e a outra metade para parte fracionária.

Figura 5. Representaçăo de 12,3456 em ponto fixo.

Figura 5. Representaçăo de 12,3456 em ponto fixo.

- Ponto Flutuante

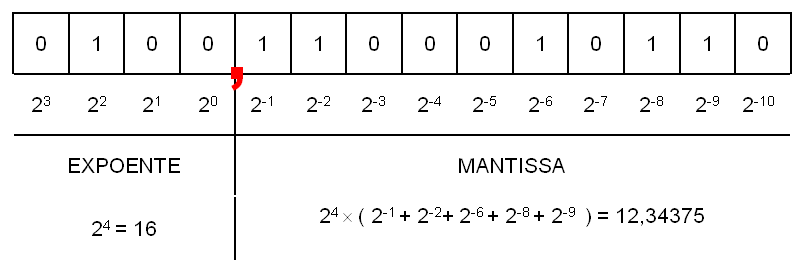

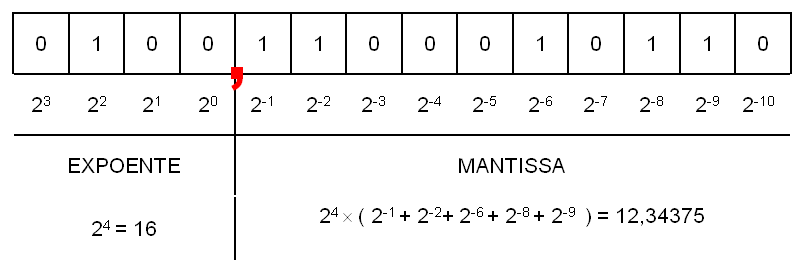

- Exemplo: representar 12,3456 em binário utilizando ponto flutuante, sendo 4 bits para o expoente e 10 bits para mantissa.

Figura 6. Representaçăo de 12,3456 em ponto flutuante.

Figura 6. Representaçăo de 12,3456 em ponto flutuante.

- Ponto Flutuante Polarizado (NĂO será utilizado nesse trabalho)

- Sistemas que utilizam o padrăo IEEE-754 usam a "polarizaçăo" para armazenar o valor do expoente. A polarizaçăo facilita a comparaçăo dos expoentes no nível lógico.

- A representaçăo com polarizaçăo NĂO será utilizada nesse trabalho.

- Normalizaçăo

- A "normalizaçăo" é utilizada para padronizar a representaçăo dos números e, também, para facilitar as operaçőes aritméticas.

Neste trabalho, um número binário será considerado normalizado quando o bit mais significativo MSB da mantissa for UM.

Se o número estiver normalizado, e o MSB for ZERO, entăo isso significa que se trata da representaçăo em ponto flutuante do valor ZERO.

0,d1d2d3...* 2e onde d1 = 1

- Exemplos de números normalizados:

- 1111 11111111 = (255/256) * 215 = 255 * 27 [Maior número representável]

- 0000 10000000 = (128/256) * 20 = 0,5 [Menor número normalizado]

- 0001 10000000 = (128/256) * 21 = 1 [Mantissa = 10000000, expoente = 1]

- 0101 10001000 = (136/256) * 25 = 17 [Mantissa = 10001000, expoente = 5]

- 11,125 = 1011,001 = 0,1011001 * 24 [Mantissa = 1011001, expoente = 4]

- 2,3125 = 10,0101 = 0,100101 * 22 [Mantissa = 100101, expoente = 2]

- 0,375 = 0,011 = 0,11 * 2-1 [Mantissa = 11000000, expoente = -1]

- 0,000 = 0 * 20 = zero [Mantissa = 00000000, expoente = 0]

- Exemplos de números NĂO normalizados:

- 11,125 = 1011,001 = 0,01011001 * 25 [Mantissa = 01011001, expoente = 5]

- 2,3125 = 10,0101 = 0,00100101 * 24 [Mantissa = 00100101, expoente = 4]

- 0,375 = 0,011 = 0,011 * 20 [Mantissa = 011, expoente = 0]

- 0,000 * 213 = zero? [Mantissa = 0, expoente = 13]

Especificaçăo

- Soluçőes em software de aritmética de ponto flutuante săo mais lentas do que soluçőes em hardware (aproximadamente 1.000 vezes mais lentas). Por essa razăo, circuitos para multiplicaçăo em ponto flutuante săo largamente utilizados em uma variedade de aplicaçőes.

- O cálculo do consumo instantâneo de combustível, realizado pelo computador de bordo de um determinado veículo, é um bom exemplo de aplicaçăo que necessita velocidade de processamento ao lidar com números em ponto flutuante.

Para calcular o consumo instantâneo de combustível săo utilizado dados provenientes de diversos sensores do veículo. É preciso obter a taxa de injeçăo de combustível, a rotaçăo do motor, a distância percorrida, a velocidade, entre outros.

Assim, diversos sensores săo lidos e cálculos săo realizados muitas vezes por segundo, de forma a manter o motorista constantemente atualizado sobre o consumo instantâneo do seu veículo.

Para facilitar a implementaçăo do circuito, assumir que o consumo instantâneo de combustível é calculado pela seguinte equaçăo:

Consumo instantâneo (km/l) = Distância percorrida * Injeçăo de combustível

- A distância percorrida e a quantidade de combustível injetado săo valores binários em ponto flutuante, calculados por um circuito dedicado, a partir de dados recebidos de sensores.

- Projetar e implementar em VHDL um circuito para o cálculo do consumo instantâneo de combustível, que utiliza como entrada as duas informaçőes da equaçăo anterior.

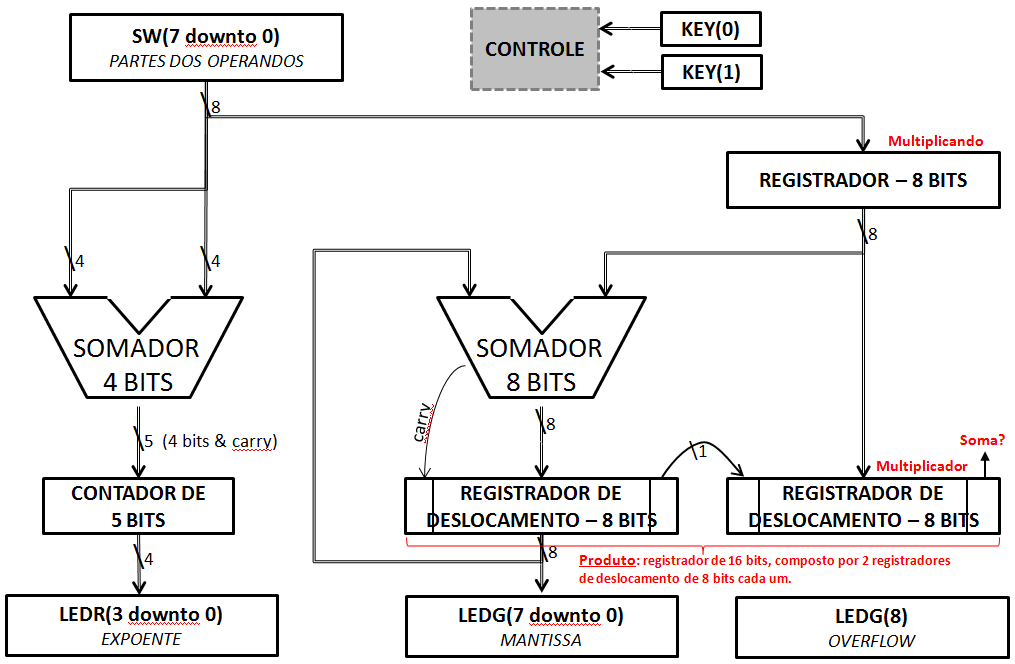

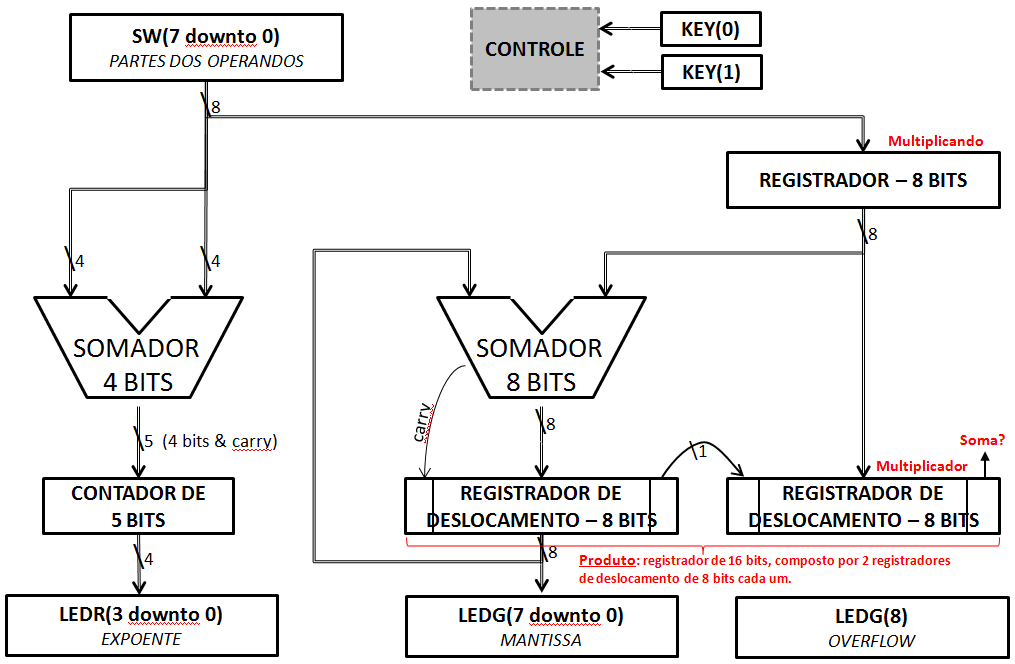

Trata-se de um circuito para multiplicaçăo em ponto flutuante, que deverá ser implementado em VHDL conforme o diagrama de blocos apresentado na Figura 7.

Figura 7. Diagrama de blocos do circuito a ser implementado em VHDL.

Figura 7. Diagrama de blocos do circuito a ser implementado em VHDL.

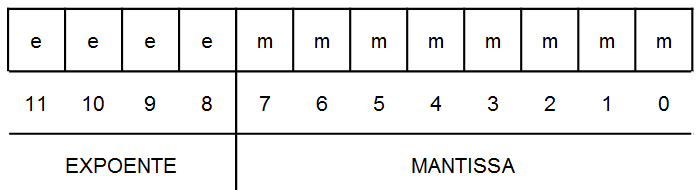

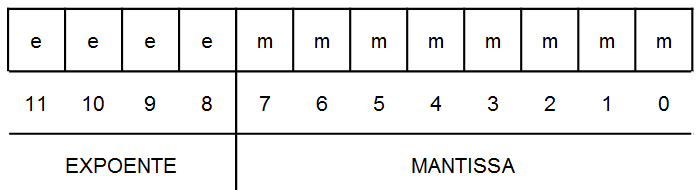

- O formato dos operandos e do resultado fornecido pelo circuito está representado na Figura 8. Nesse formato, cada valor possui 12 bits, sendo 4 bits para o expoente e 8 bits para a mantissa.

Figura 8. Formato dos operandos e resultado.

Figura 8. Formato dos operandos e resultado.

- Conforme apresentado na Figura 7, o circuito possui um total de 10 sinais (bits) de entrada, e 13 sinais (bits) de saída.

- Os 10 bits de entrada săo fornecidos por 8 chaves, SW(7 downto 0), e por dois push-buttons, KEY(0) e KEY(1), onde:

- O push-button KEY(0) deverá ser utilizado para realizar a inicializaçăo (reset) do circuito.

- O push-button KEY(1) deverá ser utilizado para alimentar o circuito com as "partes" dos operandos fornecidos por intermédio das chaves SW(7 downto 0).

- Os 13 bits de saída săo apresentados ao usuário por intermédio dos LEDs vermelhos e verdes, onde:

- Os 4 bits do expoente săo apresentados nos LEDs vermelhos LEDR(3 downto 0).

- Os 8 bits da mantissa săo apresentados nos LEDs verdes LEDG(7 downto 0).

- A ocorręncia de overflow deverá ser indicada em um LED verde - LEDG(8).

- A carga dos operandos de entrada no circuito deve ser comandada pelo push-button KEY(1) da seguinte forma:

- Ao se pressionar KEY(1) pela primeira vez, os 8 bits da mantissa do primeiro operando săo obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Ao se pressionar KEY(1) pela segunda vez, os 8 bits da mantissa do segundo operando săo obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Ao se pressionar KEY(1) pela terceira vez, os dois expoentes de 4 bits de ambos operandos săo obtidos a partir das chaves SW(7 downto 0), e carregados no circuito.

- Após KEY(1) ter sido pressionado pela terceira vez, todos os operandos foram carregados, e o circuito realiza a multiplicaçăo em ponto flutuante automaticamente, fornecendo o resultado nos LEDs vermelhos e verdes.

- Todo o controle da entrada de dados, execuçăo da multiplicaçăo em ponto flutuante, e apresentaçăo dos resultados, deve ser realizado pela máquina de estados implementada no bloco CONTROLE da Figura 7.

- Se o resultado a ser apresentado na saída (LEDs vermelhos e verdes) for diferente de zero, entăo este deverá estar normalizado, mesmo que os operandos de entrada năo estejam normalizados.

- Para realizar a normalizaçăo, será necessário deslocar a mantissa até que o primeiro dígito após a vírgula seja '1'. É preciso contar o número total de deslocamentos realizados, e alterar o expoente de acordo. Isso deve ser realizado pelo módulo "Contador de 5 bits" da Figura 7.

- Assumir que nunca irá ocorrer underflow de expoentes.

- A ocorręncia de overflow deverá ser indicada em um LED verde - LEDG(8).

- Material de apoio para o desenvolvimento do trabalho:

Documentaçăo do projeto (relatório final)

A documentaçăo deverá ser completa e clara o suficiente para possibilitar

alteraçőes e atualizaçőes na implementaçăo do projeto, sem a necessidade de consultar os

projetistas. Durante a correçăo da documentaçăo o professor da disciplina irá realizar uma

alteraçăo no código VHDL, sem consultar os autores, com informaçőes obtidas apenas a partir

da documentaçăo. Na avaliaçăo final da documentaçăo será considerado o grau de facilidade

para realizar a alteraçăo no VHDL.

A documentaçăo do projeto deverá conter uma descriçăo detalhada de todos os módulos desenvolvidos.

O texto deverá DESCREVER o projeto, sem incluir a listagem completa do código VHDL implementado.

Alguns trechos do código VHDL poderăo ser incluídos na documentaçăo, apenas quando necessário

para alguma explicaçăo de módulos implementados.

Deverá ser incluído o fluxo completo do projeto, detalhando as ferramentas utilizadas e as

etapas de projeto. A descriçăo do fluxo deve ser suficientemente detalhada de forma a

facilitar a repetiçăo de todas as etapas realizadas. No momento da correçăo do trabalho

será consultada e seguida a descriçăo do fluxo de projeto existente na documentaçăo. Dessa

forma, descriçőes incompletas do fluxo de projeto poderăo prejudicar a avaliaçăo do trabalho.

Preparar e incluir na documentaçăo um diagrama de blocos completo com todos os módulos implementados.

O diagrama de blocos deverá ser detalhado de forma a incluir todos os sinais de entrada e saída,

e todos os módulos implementados.

Deverá ser fornecida também a representaçăo gráfica das máquinas de estados, tabelas de estados e

explicaçőes sobre estados e transiçőes.

Sugestăo de organizaçăo para o documento do projeto:

- Folha de rosto contendo dados do autor, da instituiçăo, local, data;

- Objetivos do trabalho;

- Especificaçăo do problema proposto - visăo/entendimento do autor sobre essa especificaçăo;

- Projeto dos componentes do sistema com uma breve descriçăo do objetivo de cada componente.

Incluir nessa descriçăo uma explicaçăo (com diagrama de blocos e textual) dos componentes

estudados na teoria e sua utilizaçăo na prática (ex. multiplexadores, decodificadores, circuitos

aritméticos, ...);

- Descriçăo das ferramentas utilizadas e fluxo de projeto;

- Descriçăo da simulaçăo realizada, com diagramas de forma de ondas extraídos diretamente do Quartus II ou ModelSim;

- Consideraçőes e conclusőes sobre o trabalho realizado.

É importante cuidar a coeręncia e a coesăo da documentaçăo, pois o documento entregue será

essencial para o entendimento e correçăo do trabalho realizado.

A documentaçăo deverá ser entregue no Moodle,

obedecendo RIGOROSAMENTE o prazo estipulado.

Código fonte VHDL e arquivo de projeto do Quartus II

O código fonte VHDL deve estar adequadamente comentado - incluir um comentário explicativo em cada

bloco de código e, sempre que necessário, em linhas individuais.

Incluir um bloco de comentário no início do arquivo com o fonte VHDL contendo

dados dos alunos e demais dados de identificaçăo do projeto (ex. utilidade, ferramentas, FPGA alvo, ...).

O código fonte precisa estar com a indentaçăo adequada.

Escolher nomes adequados para os símbolos utilizados no programa (entities, architectures, signals, ...).

Os fontes VHDL deverăo ser entregues no Moodle, obedecendo RIGOROSAMENTE o prazo estipulado.

Gerar um arquivo compactado, contendo APENAS os fontes VHDL do projeto desenvolvido no Quartus II, e submeter apenas esse arquivo. O sistema de submissăo de trabalhos disponível no Moodle aceitará a submissăo de um único arquivo por grupo.

Etapas do projeto e dicas úteis

1. Dividir o problema em partes menores - abordagem "dividir para conquistar":

Desenvolver circuitos em VHDL para acesso aos periféricos da placa com o FPGA. Durante o semestre,

alguns desses circuitos foram desenvolvidos nas aulas teóricas e práticas como, por exemplo, registradores e máquinas de estados.

Desenvolver circuitos combinacionais em VHDL para as operaçőes lógicas e aritméticas a serem executadas.

Seguir as dicas para implementaçăo de circuitos controladores fornecidas

nas aulas teóricas e práticas. Uma boa dica de descriçăo em VHDL de uma FSM de controlador

é desenvolvida no Laboratório 9.

Após ter certeza que todos os circuitos possuem o comportamento desejado, realizar a integraçăo dos

componentes desenvolvidos, formando gradualmente sistemas digitais mais completos que atendam aos

requisitos fornecidos. A integraçăo de componentes é discutida no Lab 6 (port map).

Seguindo essa filosofia de projeto, poderia ser desenvolvida uma versăo inicial do projeto com apenas uma

funcionalidade, por exemplo, e após devidamente validada, as demais funcionalidades poderiam

ser incluídas (todos os novos componentes sendo validados individualmente, antes de serem

anexados ao projeto).

ATENÇĂO!! Mesmo projetistas de sistemas digitais experientes, já atuando na

indústria, năo desenvolvem sistemas por inteiro sem antes simular e validar os componentes

individualmente. Essa regra é seguida por projetistas experientes até para sistemas digitais

considerados simples como, por exemplo, o projeto em questăo.

2. Simulaçăo do projeto:

Utilizar ferramentas de simulaçăo com formas de ondas, tais como, o ModelSim ou o Quartus II para simular os circuitos

desenvolvidos individualmente.

Realizar a simulaçăo com os diagramas de formas de ondas dos diversos componentes desenvolvidos e,

gradualmente, dos novos componentes compostos pela integraçăo dos componentes menores, até chegar

na implementaçăo final do projeto.

3. Prototipaçăo no kit com FPGA:

Identificar os periféricos disponíveis no kit de desenvolvimento e pinos de entrada/saída, que poderăo ser úteis

no desenvolvimento do sistema digital solicitado. Informaçőes sobre pinos e periféricos poderăo ser

encontradas no Manual do Usuário da Placa DE2, ou

no manual do usuário de algum outro kit selecionado para o projeto.

Testar no FPGA os diversos componentes conforme forem sendo desenvolvidos, assim como os componentes

resultantes da integraçăo dos módulos. Realizar os testes na placa, apenas após a simulaçăo indicar

que o sistema está funcionando de acordo com o esperado.

Os kits de ensino do laboratório năo poderăo ser emprestados para os alunos, que deverăo compartilhar os mesmos apenas no

laboratório.

4. Ajuda:

Procurar o monitor da disciplina para dúvidas sobre o projeto dos circuitos a serem utilizados.

Verificar as agendas semanais dos professores da disciplina para agendar horários de atendimento e, também,

para agendar a data/hora da apresentaçăo do trabalho que deverá ser realizada na semana que inicia no dia 28 de novembro:

Avaliaçăo

O trabalho poderá ser desenvolvido individualmente ou em grupos com, no máximo, tręs integrantes.

A documentaçăo do projeto e o fonte VHDL deverăo ser entregues no Moodle no dia 25 de novembro de 2011.

A apresentaçăo da simulaçăo e a demonstraçăo do funcionamento por intermédio de simulaçăo será realizada

na semana de 28 de novembro a 02 de dezembro 2011. O grupo deverá agendar

a data e hora para apresentaçăo do trabalho durante essa semana.

Durante a apresentaçăo, os alunos deverăo estar aptos a responder quaisquer perguntas. Respostas

insatisfatórias ou a ausęncia dos alunos poderá acarretar em anulaçăo da nota final.

Na apresentaçăo serăo realizados questionamentos sobre decisőes de projeto e estratégias

de implementaçăo VHDL utilizadas. Será verificada também a familiaridade dos alunos com

as ferramentas de desenvolvimento utilizadas durante o semestre. Todos os alunos do grupo

devem estar aptos a responder todas as questőes.

As explicaçőes durante a apresentaçăo da documentaçăo do projeto, e na demonstraçăo do projeto

funcionando por intermédio da simulaçăo e dos diagramas de formas de onda, săo fundamentais

para a avaliaçăo.

Trabalhos copiados, inclusive entre turmas, resultarăo em nota zero para todos os alunos envolvidos.

Será utilizado o MOSS como ferramenta auxiliar

na identificaçăo de situaçőes de plágio.

Os dois itens a serem avaliados possuem os seguintes pesos na nota final do trabalho prático:

OBSERVAÇĂO IMPORTANTE!! O trabalho poderá ser realizado em grupo, porém A AVALIAÇĂO É INDIVIDUAL. Cada integrante do grupo SERÁ QUESTIONADO

INDIVIDUALMENTE, e deverá estar apto A UTILIZAR A FERRAMENTA de desenvolvimento, e mostrar CONHECIMENTO DE TODO O VHDL desenvolvido, assim como da SIMULAÇĂO REALIZADA.