- Low Standby-Current Consumption of 10 μA Maximum

- I<sup>2</sup>C to Parallel-Port Expander

- Open-Drain Interrupt Output

- Compatible With Most Microcontrollers

- Latched Outputs With High-Current Drive Capability for Directly Driving LEDs

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

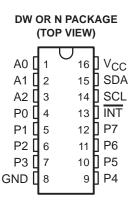

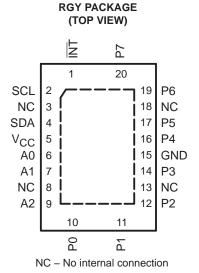

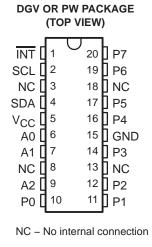

#### description/ordering information

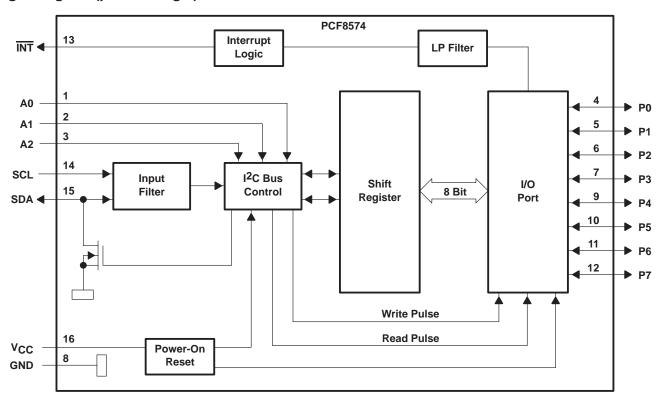

This 8-bit input/output (I/O) expander for the two-line bidirectional bus (I $^2$ C) is designed for 2.5-V to 6-V V $_{CC}$  operation.

The PCF8574 provides general-purpose remote I/O expansion for most microcontroller families via the I<sup>2</sup>C interface [serial clock (SCL), serial data (SDA)].

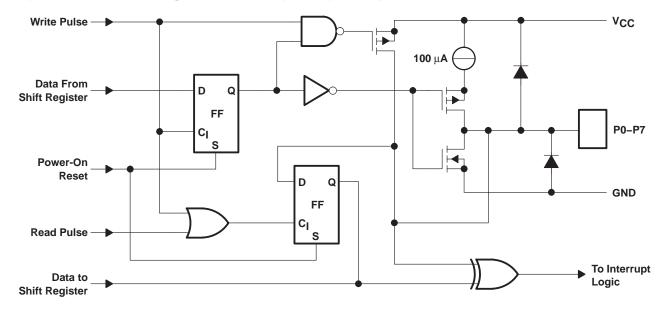

The device features an 8-bit quasi-bidirectional I/O port (P0–P7), including latched outputs with high-current drive capability for directly driving LEDs. Each quasi-bidirectional I/O can be used as an input or output without the use of a data-direction control signal. At power on, the I/Os are high. In this mode, only a current source to  $V_{CC}$  is active. An additional strong pullup to  $V_{CC}$  allows fast rising edges into heavily loaded outputs. This device turns on when an output is written high and is switched off by the negative edge of SCL. The I/Os should be high before being used as inputs.

#### ORDERING INFORMATION

| TA            | PACKAGE†    |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|-------------|---------------|--------------------------|---------------------|

|               | QFN – RGY   | Tape and reel | PCF8574RGYR              | PF574               |

|               | PDIP – N    | Tube          | PCF8574N                 | PCF8574N            |

| 4000 to 0500  | SOIC - DW   | Tube          | PCF8574DW                | DOE0574             |

| -40°C to 85°C |             | Tape and reel | PCF8574DWR               | PCF8574             |

|               | TSSOP – PW  | Tape and reel | PCF8574PWR               | PF574               |

|               | TVSOP - DGV | Tape and reel | PCF8574DGVR              | PF574               |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCPS068C - JULY 2001 - REVISED JANUARY 2004

## description/ordering information (continued)

The PCF8574 provides an open-drain output ( $\overline{\text{INT}}$ ) that can be connected to the interrupt input of a microcontroller. An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time  $t_{\text{IV}}$ ,  $\overline{\text{INT}}$  is valid. Resetting and reactivating the interrupt circuit is achieved when data on the port is changed to the original setting or data is read from, or written to, the port that generated the interrupt. Resetting occurs in the read mode at the acknowledge bit after the rising edge of the SCL signal or in the write mode at the acknowledge bit after the high-to-low transition of the SCL signal. Interrupts that occur during the acknowledge clock pulse can be lost (or be very short) due to the resetting of the interrupt during this pulse. Each change of the I/Os after resetting is detected and, after the next rising clock edge, is transmitted as  $\overline{\text{INT}}$ . Reading from, or writing to, another device does not affect the interrupt circuit.

By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C bus. Therefore, the PCF8574 can remain a simple slave device.

#### logic diagram (positive logic)

Pin numbers shown are for the DW and N packages.

### simplified schematic diagram of each P-port input/output

#### I<sup>2</sup>C interface

I<sup>2</sup>C communication with this device is initiated by a master sending a start condition, a high-to-low transition on the SDA I/O while the SCL input is high. After the start condition, the device address byte is sent, most-significant bit (MSB) first, including the data direction bit (R $\overline{\text{W}}$ ). This device does not respond to the general call address. After receiving the valid address byte, this device responds with an acknowledge, a low on the SDA I/O during the high of the acknowledge-related clock pulse. The address inputs (A0–A2) of the slave device must not be changed between the start and the stop conditions.

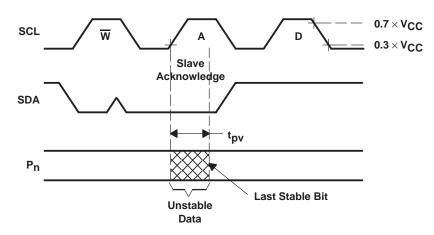

The data byte follows the address acknowledge. If the  $R/\overline{W}$  bit is high, the data from this device are the values read from the P port. If the  $R/\overline{W}$  bit is low, the data are from the master, to be output to the P port. The data byte is followed by an acknowledge sent from this device. If other data bytes are sent from the master, following the acknowledge, they are ignored by this device. Data are output only if complete bytes are received and acknowledged. The output data will be valid at time  $t_{pv}$  after the low-to-high transition of SCL and during the clock cycle for the acknowledge.

A stop condition, which is a low-to-high transition on the SDA I/O while the SCL input is high, is sent by the master.

#### INTERFACE DEFINITION

| DVTE                           | BIT     |    |    |    |    |    |    |         |

|--------------------------------|---------|----|----|----|----|----|----|---------|

| BYTE                           | 7 (MSB) | 6  | 5  | 4  | 3  | 2  | 1  | 0 (LSB) |

| I <sup>2</sup> C slave address | L       | Н  | L  | L  | A2 | A1 | AO | R/W     |

| I/O data bus                   | P7      | P6 | P5 | P4 | P3 | P2 | P1 | P0      |

#### ADDRESS REFERENCE

| INPUTS |    |    | I <sup>2</sup> C-BUS SLAVE ADDRESS |  |  |

|--------|----|----|------------------------------------|--|--|

| A2     | A1 | Α0 | I <sup>2</sup> C-BUS SLAVE ADDRESS |  |  |

| L      | L  | L  | 32 (decimal), 20 (hexadecimal)     |  |  |

| L      | L  | Н  | 33 (decimal), 21 (hexadecimal)     |  |  |

| L      | Н  | L  | 34 (decimal), 22 (hexadecimal)     |  |  |

| L      | Н  | Н  | 35 (decimal), 23 (hexadecimal)     |  |  |

| Н      | L  | L  | 36 (decimal), 24 (hexadecimal)     |  |  |

| Н      | L  | Н  | 37 (decimal), 25 (hexadecimal)     |  |  |

| Н      | Н  | L  | 38 (decimal), 26 (hexadecimal)     |  |  |

| Н      | Н  | Н  | 39 (decimal), 27 (hexadecimal)     |  |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range V                                               | 0 E \/ to 7 \/               |

|----------------------------------------------------------------------|------------------------------|

| Supply voltage range, V <sub>CC</sub>                                |                              |

| Input voltage range, V <sub>I</sub> (see Note 1)                     |                              |

| Output voltage range, V <sub>O</sub> (see Note 1)                    | $-0.5$ V to $V_{CC} + 0.5$ V |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)            | –20 mA                       |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)           |                              |

| Input/Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ ) | ±400 μA                      |

| Continuous output low current, $I_{OL}$ ( $V_O = 0$ to $V_{CC}$ )    | 50 mA                        |

| Continuous output high current, $I_{OH}$ ( $V_O = 0$ to $V_{CC}$ )   |                              |

| Continuous current through V <sub>CC</sub> or GND                    | ±100 mA                      |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2): DGV package | 92°C/W                       |

| (see Note 2): DW package                                             | 57°C/W                       |

| (see Note 2): N package                                              | 67°C/W                       |

| (see Note 2): PW package                                             | 83°C/W                       |

| (see Note 3): RGY package                                            | 37°C/W                       |

| Storage temperature range, T <sub>stg</sub>                          | –65°C to 150°C               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 2. The package thermal impedance is calculated in accordance with JESD 51-7.

- 3. The package thermal impedance is calculated in accordance with JESD 51-5.

## recommended operating conditions

|                 |                                | MIN                 | MAX                   | UNIT |

|-----------------|--------------------------------|---------------------|-----------------------|------|

| VCC             | Supply voltage                 | 2.5                 | 6                     | V    |

| VIH             | High-level input voltage       | $0.7 \times V_{CC}$ | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub> | Low-level input voltage        | -0.5                | $0.3 \times V_{CC}$   | V    |

| lOH             | High-level output current      |                     | -1                    | mA   |

| loL             | Low-level output current       |                     | 25                    | mA   |

| TA              | Operating free-air temperature | -40                 | 85                    | °C   |

SCPS068C - JULY 2001 - REVISED JANUARY 2004

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                       | TEST CONDITIONS                                        | Vcc          | MIN  | TYP <sup>†</sup> | MAX  | UNIT |  |

|------------------|---------------------------------|--------------------------------------------------------|--------------|------|------------------|------|------|--|

| VIK              | Input diode clamp voltage       | I <sub>I</sub> = -18 mA                                | 2.5 V to 6 V | -1.2 |                  |      | V    |  |

| VPOR             | Power-on reset voltage‡         | $V_I = V_{CC}$ or GND, $I_O = 0$                       | 6 V          |      | 1.3              | 2.4  | V    |  |

| Іон              | P port                          | V <sub>O</sub> = GND                                   | 2.5 V to 6 V | 30   |                  | 300  | μΑ   |  |

| IOHT             | P-port transient pullup current | High during acknowledge VOH = GND                      | 2.5 V        |      | -1               |      | mA   |  |

|                  | SDA                             | V <sub>O</sub> = 0.4 V                                 | 2.5 V to 6 V | 3    |                  |      |      |  |

| lOL              | P port                          | V <sub>O</sub> = 1 V                                   | 5 V          | 10   | 25               |      | mA   |  |

|                  | INT                             | V <sub>O</sub> = 0.4 V                                 | 2.5 V to 6 V | 1.6  |                  |      |      |  |

|                  | SCL, SDA                        |                                                        |              |      |                  | ±5   |      |  |

| l <sub>l</sub>   | INT                             | V <sub>I</sub> = V <sub>CC</sub> or GND                | 2.5 V to 6 V |      |                  | ±5   | μΑ   |  |

|                  | A0, A1, A2                      |                                                        |              |      |                  | ±5   |      |  |

| I <sub>IHL</sub> | P port                          | $V_1 \ge V_{CC}$ or $V_1 \le GND$                      | 2.5 V to 6 V |      |                  | ±400 | μΑ   |  |

|                  | Operating mode                  | $V_I = V_{CC}$ or GND, $I_O = 0$ , $f_{SCL} = 100$ kHz | 5.14         |      | 40               | 100  |      |  |

| ICC              | Standby mode                    | $V_I = V_{CC}$ or GND, $I_O = 0$                       | 6 V          |      | 2.5              | 10   | μΑ   |  |

| Ci               | SCL                             | $V_I = V_{CC}$ or GND                                  | 2.5 V to 6 V |      | 1.5              | 7    | pF   |  |

|                  | SDA                             | V V 0ND                                                | 2.5 V to 6 V |      | 3                | 7    |      |  |

| C <sub>io</sub>  | P port                          | V <sub>IO</sub> = V <sub>CC</sub> or GND               |              |      | 4                | 10   | pF   |  |

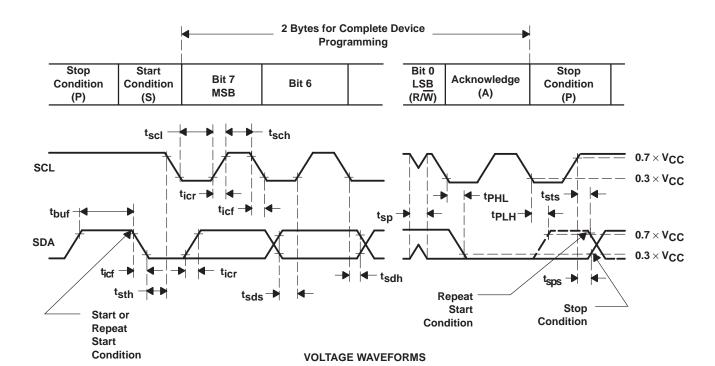

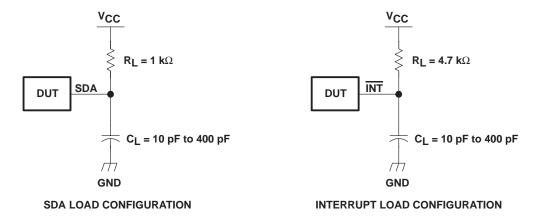

## $I^2C$ interface timing requirements over recommended operating free-air temperature range (unless otherwise noted) (see Figure 1)

|                  |                                                          |                             | MIN | MAX | UNIT |

|------------------|----------------------------------------------------------|-----------------------------|-----|-----|------|

| f <sub>scl</sub> | I <sup>2</sup> C clock frequency                         |                             |     | 100 | kHz  |

| tsch             | I <sup>2</sup> C clock high time                         |                             | 4   |     | μs   |

| t <sub>scl</sub> | I <sup>2</sup> C clock low time                          |                             | 4.7 |     | μs   |

| t <sub>SP</sub>  | I <sup>2</sup> C spike time                              |                             |     | 100 | ns   |

| t <sub>sds</sub> | I <sup>2</sup> C serial data setup time                  |                             | 250 |     | ns   |

| tsdh             | I <sup>2</sup> C serial data hold time                   |                             | 0   | 900 | ns   |

| ticr             | I <sup>2</sup> C input rise time                         |                             |     | 1   | μs   |

| ticf             | I <sup>2</sup> C input fall time                         |                             |     | 0.3 | μs   |

| tocf             | I <sup>2</sup> C output fall time (10-pF to 400-pF bus)  |                             |     | 300 | ns   |

| tbuf             | I <sup>2</sup> C-bus free time between stop and start    |                             | 4.7 |     | μs   |

| t <sub>sts</sub> | I <sup>2</sup> C start or repeated start condition setup |                             | 4.7 |     | μs   |

| tsth             | I <sup>2</sup> C start or repeated start condition hold  |                             | 4   |     | μs   |

| t <sub>sps</sub> | I <sup>2</sup> C stop-condition setup                    |                             | 4   |     | μs   |

| t <sub>vd</sub>  | Valid data time                                          | SCL low to SDA output valid |     | 3.4 | μs   |

| C <sub>b</sub>   | I <sup>2</sup> C-bus capacitive load                     |                             |     | 400 | pF   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. ‡ The power-on reset circuit resets the I<sup>2</sup>C-bus logic with V<sub>CC</sub> < V<sub>POR</sub> and sets all I/Os to logic high (with current source to V<sub>CC</sub>).

## PCF8574 REMOTE 8-BIT I/O EXPANDER FOR I<sup>2</sup>C BUS

SCPS068C - JULY 2001 - REVISED JANUARY 2004

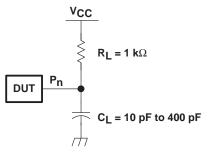

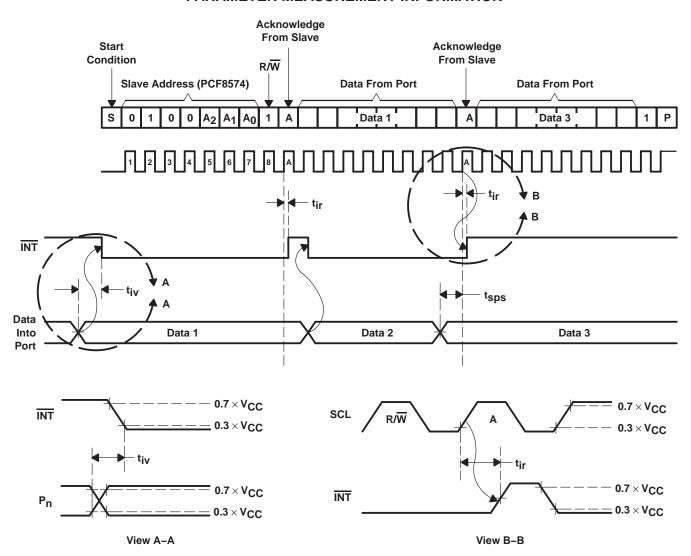

# switching characteristics over recommended operating free-air temperature range, $C_L \leq 100~pF$ (unless otherwise noted) (see Figure 2)

|                 | PARAMETER                  | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN | MAX | UNIT |

|-----------------|----------------------------|-----------------|----------------|-----|-----|------|

| tpv             | Output data valid          | SCL             | P port         |     | 4   | μs   |

| t <sub>su</sub> | Input data setup time      | P port          | SCL            | 0   |     | μs   |

| th              | Input data hold time       | P port          | SCL            | 4   |     | μs   |

| tiv             | Interrupt valid time       | P port          | INT            |     | 4   | μs   |

| t <sub>ir</sub> | Interrupt reset delay time | SCL             | INT            |     | 4   | μs   |

#### PARAMETER MEASUREMENT INFORMATION

LOAD CIRCUIT

| BYTE | DESCRIPTION              |

|------|--------------------------|

| 1    | I <sup>2</sup> C address |

| 2    | P-port data              |

Figure 1. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

#### PARAMETER MEASUREMENT INFORMATION

Figure 2. Interrupt-Timing Waveforms

## PARAMETER MEASUREMENT INFORMATION

Figure 3. Write-Mode Timing

Figure 4. Load Circuits

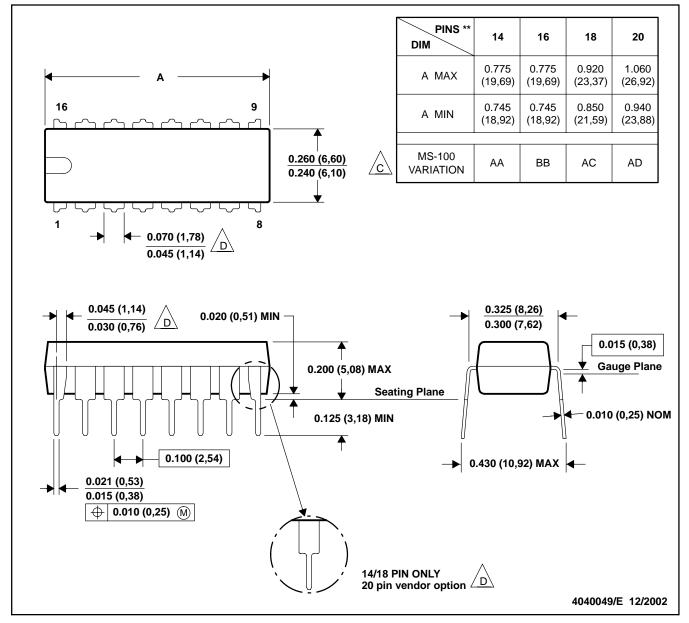

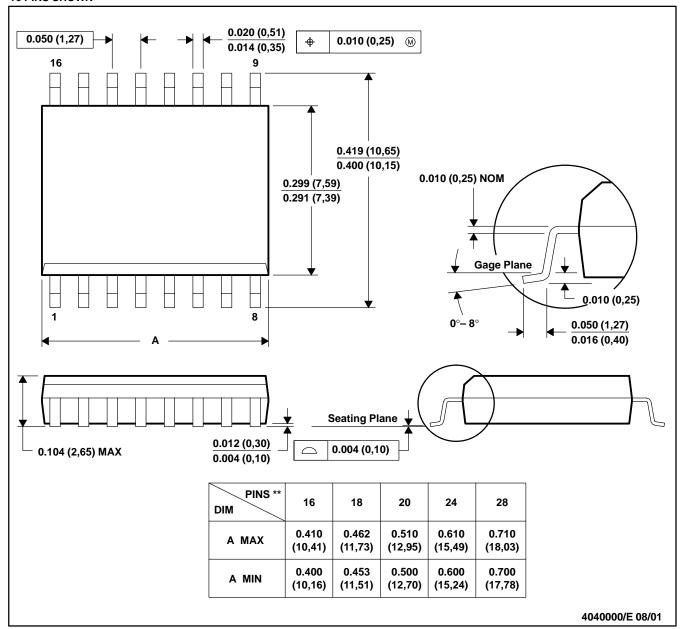

#### N (R-PDIP-T\*\*)

#### **16 PINS SHOWN**

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

Falls within JEDEC MS-001, except 18 and 20 pin minimum body Irngth (Dim A).

The 20 pin end lead shoulder width is a vendor option, either half or full width.

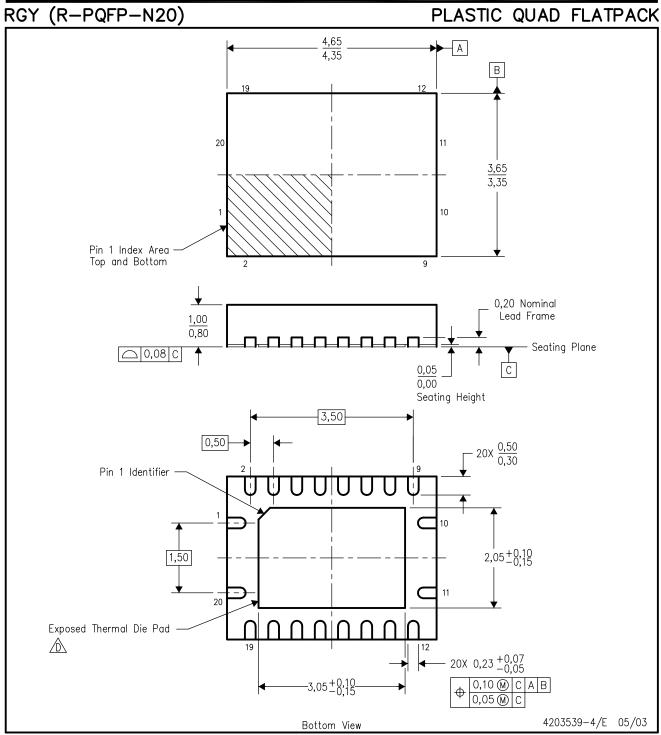

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) package configuration.

- The package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected ground leads.

- E. Package complies to JEDEC MO-241 variation BC.

#### DW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### **16 PINS SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013

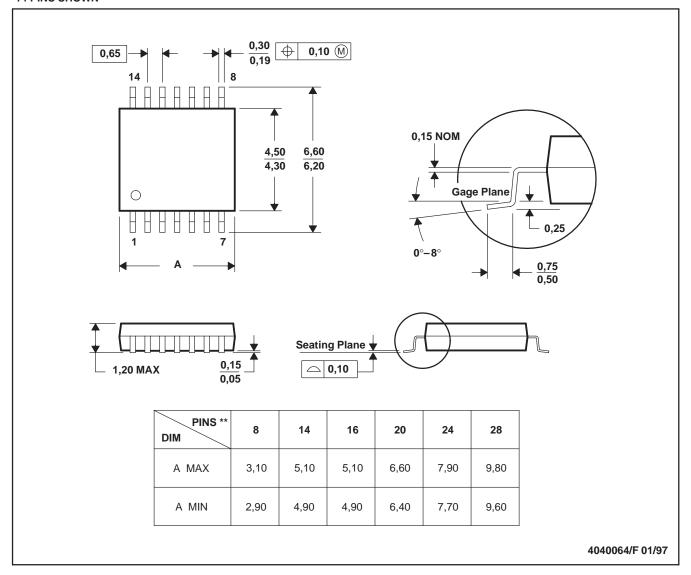

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated